# DOSonCHIP™

# Memory Card Interface with File System

#### **GENERAL DESCRIPTION**

The DOSonCHIP<sup>TM</sup> CD17B10 provides an interface to industry standard removable memory cards, including microSDHC, microSD, miniSDHC, miniSD, SDHC, SD, and MMC cards. Both a physical interface and file system interface are included on the CD17B10. Simple file commands along with user data are sent to the CD17B10 over either of its UART, SPI, or I<sup>2</sup>C/SMBbus<sup>†</sup>. These file commands are used to navigate the file system directory, read data, or write data to the memory card using the industry standard FAT file system format, which is directly compatible with PC's, digital media players, digital cameras, etc.

#### **F**EATURES

- UART / SPI / I<sup>2</sup>C/SMBus<sup>†</sup> to microSDHC / microSD / miniSDHC / miniSD / SDHC / SD / MMC memory card interface

- Hot swap of memory card

- FAT16 / FAT32 file system compatible

- Minimal external components

- Real Time Clock with file time-stamping

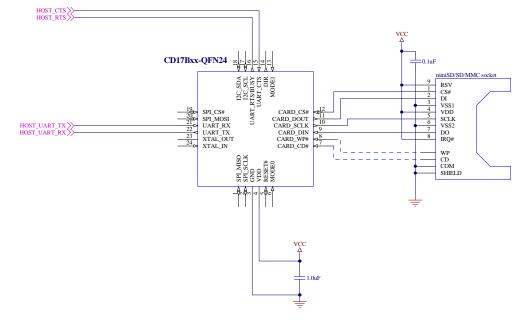

#### **TYPICAL APPLICATION CIRCUIT**

- 4 simultaneous open files

- 2.7V 3.3V operation

- 5V tolerant I/O

- 5mA typical operating current

- 0.1µA typical shutdown current

- In System Upgradable

- Small PCB real estate: 4mm x 4mm

**CD17B10**

- Simplified PCB layout

- -40 to +85 °C Temperature Range

- RoHS compliant

#### PACKAGES

- 24-pin QFN

- 32-pin QFP

#### **APPLICATIONS**

- Portable Consumer Electronics

- Mobile Handsets

- Digital Audio/Video Players

- Digital Cameras

- Laptop and Palm Computers

- Media Players

- Scientific Data Loggers

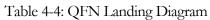

Typical Application Circuit (UART interface)

# **Table of Contents**

| 1.  | System Overview                           | 3  |

|-----|-------------------------------------------|----|

| 2.  | Absolute Maximum Ratings                  | 4  |

| 3.  | <b>DC Electrical Characteristics</b>      | 5  |

| 4.  | Pinout and Package Definitions            | 7  |

| 5.  | <b>Reset &amp; Power-Up Configuration</b> | 12 |

| 6.  | <b>Communication Ports</b>                | 13 |

| 7.  | Real Time Clock (RTC)                     | 18 |

| 8.  | In-System Updates                         | 19 |

| 9.  | Ordering Information                      | 19 |

| 10. | Document Change List                      | 25 |

| 11. | Contact Information                       | 26 |

### 1. System Overview

CD17B10 devices are fully integrated memory card controllers with a high-level file system stack. The CD17B10 devices contain a complete host serial interface to memory card physical interface. Reading and writing PC compatible files from/to widely available memory cards is executed using simple commands while retaining complete PC compatibility. Also included is the optional real-time clock (RTC) for keeping the current date and time and for time-stamping files. Finally, in-system firmware updating is available to provide new capabilities and future optimizations.

The host communications interface consists of either: UART, SPI, or I<sup>2</sup>C/SMBus<sup>†</sup> serial interface. This interface accepts commands and data from the host and responds with status and data appropriately. Please see the DOSonCHIP host source code for command protocol and syntax.

The memory card physical layer interface is compatible with industry standard Secure Digital (SD) cards, Secure Digital High Capacity (SDHC) cards, and the Multi-Memory cards (MMC). The physical interface provides hot-swapping of memory cards and is designed to provide a simple PCB layout.

The file system stack is based upon the PC compatible FAT file system. Both FAT16 and FAT32 standards are supported. Reading, writing, and file/folder management is provided along with clock and interface option settings. Please see the DOSonCHIP host source code for the available commands.

The optional real-time clock (RTC) provides time keeping with date and leap year correction. This function is useful for tracking the last time a file was modified or created. The date and time is also available to the host for standard time-keeping functionality. This option is contingent with adding an external watch crystal.

The CD17B10 devices allow for in-system firmware upgrading. This allows future-proofing as well as the ability to add new and customized firmware capabilities.

### 2. Absolute Maximum Ratings

| Parameter                                                                                                                                                                                                                                                                                                             | Conditions | Min  | Тур | Max | Units |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------|-----|-----|-------|--|--|

| Ambient temperature under bias                                                                                                                                                                                                                                                                                        |            | -55  | _   | 125 | °C    |  |  |

| Storage Temperature                                                                                                                                                                                                                                                                                                   |            | -65  | _   | 150 | °C    |  |  |

| Voltage on any I/O pin or RESET# with respect to GND                                                                                                                                                                                                                                                                  |            | -0.3 | _   | 5.8 | V     |  |  |

| Voltage on VDD with respect to GND                                                                                                                                                                                                                                                                                    |            | -0.3 | _   | 4.2 | V     |  |  |

| Maximum Total current through VDD and GND                                                                                                                                                                                                                                                                             |            | _    | _   | 500 | mA    |  |  |

| Maximim output current sunk by RESET# or any I/O pin                                                                                                                                                                                                                                                                  |            | _    | _   | 100 | mA    |  |  |

| *Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the devices at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to |            |      |     |     |       |  |  |

Table 2-1: Absolute Maximum Ratings\*

maximum rating conditions for extended periods may affect device reliability.

### **3. DC Electrical Characteristics**

-40 to +85 °C unless otherwise specified

| Parameter                                | Conditions | Min               | Тур | Max | Units |  |

|------------------------------------------|------------|-------------------|-----|-----|-------|--|

| Supply Voltage                           |            | VRST <sup>1</sup> | 3.0 | 3.6 | V     |  |

| Supply Current: Active                   | VDD = 2.7V | _                 | 5.0 | Ι   | mA    |  |

| Supply Current Inactive                  |            | _                 | 3.2 |     | mA    |  |

| Supply Current Shutdown                  |            | _                 | 0.1 | Ι   | μΑ    |  |

| Supply RAM Data Retention Voltage        |            | _                 | 1.5 | _   | V     |  |

| Specified Operating Temperature<br>Range | Industrial | -40               | _   | +85 | °C    |  |

| Notes:                                   |            |                   |     |     |       |  |

| 1. Given in Table 2-1.                   |            |                   |     |     |       |  |

Table 3-2: Reset Electrical Characteristics

-40 to +85 °C unless otherwise specified

| Parameter                                             | Conditions                          | Min       | Тур  | Max          | Units |

|-------------------------------------------------------|-------------------------------------|-----------|------|--------------|-------|

| RESET# Output Low Voltage                             | IOL = 8.5 mA, VDD = 2.7<br>to 3.6 V | _         | _    | 0.6          | V     |

| RESET# Input High Voltage                             |                                     | 0.7 x VDD | _    | _            | V     |

| RESET# Input Low Voltage                              |                                     | _         | _    | 0.3 x<br>VDD | V     |

| RESET# Input Pullup Current                           | RESET # = 0.0V                      | _         | 25   | 40           | μА    |

| VDD Monitor Threshold (VRST)                          |                                     | 2.40      | 2.55 | 2.70         | V     |

| Minimum RESET# Low Time to<br>Generate a System Reset |                                     | 15        | _    | _            | μs    |

| VDD Ramp Time                                         | VDD = 0 to $VDD = 2.7V$             | _         | _    | 1            | ms    |

Table 3-3: Port I/O DC Electrical Characteristics

VDD = 2.7 to 3.6 V, -40 to +85 °C unless otherwise specified

| Parameter             | Conditions                              | Min       | Тур       | Max | Units |

|-----------------------|-----------------------------------------|-----------|-----------|-----|-------|

|                       | IOH = -3 mA, Port I/O push-pull         | VDD - 0.7 | _         | _   |       |

| Output High Voltage   | $IOH = -10 \mu A$ , Port I./O push-pull | VDD - 0.1 | _         | _   | V     |

|                       | IOH = -10  mA, Port I./O push-pull      | _         | VDD – 0.8 | _   |       |

|                       | IOL = 8.5  mA                           | -         | _         | 0.6 |       |

| Output Low Voltage    | $IOL = 10 \mu A$                        | _         | _         | 0.1 | V     |

|                       | IOL = 8.5  mA                           | _         | 1.0       | _   |       |

| Input High Voltage    |                                         | 2.0       | _         | _   | V     |

| Input Low Voltage     |                                         | _         | _         | 0.8 | V     |

| Input Leakage Current | VIN = 0 V                               | _         | 25        | 40  | μΑ    |

## **4. Pinout and Package Definitions**

| Name          | Pin Numbers |     | Туре   | Description                                                                                                                                                              |

|---------------|-------------|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | QFP         | QFN |        |                                                                                                                                                                          |

| VDD           | 4           | 4   | Power  | Power Supply Voltage.                                                                                                                                                    |

| GND           | 3           | 3   | Power  | Ground.                                                                                                                                                                  |

| RESET#        | 5           | 5   | D I/O  | Device Reset. External Reset input and open<br>drain output of internal power-on reset & VDD<br>Brownout Reset. Drive low for at least 10µs to<br>manually reset device. |

| MODE0         | 6           | 6   | DI     | Device Com Port Select 0. Used in conjunction<br>with MODE1 pin. See rest of datasheet for<br>details.                                                                   |

| SPI_SCLK      | 2           | 2   | DI     | SPI Slave Port Clock Input.                                                                                                                                              |

| SPI_MISO      | 1           | 1   | DO     | SPI Slave Port Data Output.                                                                                                                                              |

| XTAL_IN       | 32          | 24  | A In   | External Clock Input. Connect to watch crystal<br>for Real Time Clock function; otherwise leave<br>unconnected or connect to Ground.                                     |

| XTAL_OUT      | 31          | 23  | A Out  | External Clock Output. Connect to crystal for<br>Real Time Clock function; otherwise do not<br>connect.                                                                  |

| UART_TX       | 30          | 22  | DO     | Asynchronous Transmitter Output.                                                                                                                                         |

| UART_RX       | 29          | 21  | DI     | Asynchronous Transmitter Input.                                                                                                                                          |

| SPI_MOSI      | 28          | 20  | DI     | SPI Slave Port Data Input.                                                                                                                                               |

| SPI_CS#       | 27          | 19  | DI     | SPI Slave Port Chip Select.                                                                                                                                              |

| I2C_SDA       | 26          | 18  | D I/OC | I <sup>2</sup> C /SMBus Slave Port Data.                                                                                                                                 |

| I2C_SCL       | 25          | 17  | D I/OC | I <sup>2</sup> C /SMBus Slave Port Clock.                                                                                                                                |

| UART_RTS/BUSY | 24          | 16  | DO     | Request To Send Output /Busy Output.                                                                                                                                     |

| UART_CTS      | 23          | 15  | DI     | Clear To Send Input.                                                                                                                                                     |

Table 4-1: Pin Definitions

| Name      | Pin Numbers |     | Туре  | Description                                                                                            |

|-----------|-------------|-----|-------|--------------------------------------------------------------------------------------------------------|

|           | QFP         | QFN |       |                                                                                                        |

| DIR       | 22          | 14  | DI    | Direction. Used to indicate data direction for host-chip communications.                               |

| MODE1     | 21          | 13  | DI    | Device Com Port Select 1. Used in conjunction<br>with MODE0 pin. See rest of datasheet for<br>details. |

| RSVD1     | 20          | _   |       | Reserved Pin 1. Do not connect                                                                         |

| RSVD2     | 19          | _   |       | Reserved Pin 2. Do not connect                                                                         |

| CARD_CS#  | 18          | 12  | DI    | Memory Card Select/Detect.                                                                             |

| CARD_DOUT | 17          | 11  | DO    | Memory Card Data Output.                                                                               |

| CARD_SCK  | 16          | 10  | DO    | Memory Card Clock Output.                                                                              |

| CARD_DIN  | 15          | 9   | D I/O | Memory Card Data Input.                                                                                |

| CARD_WP   | 14          | 8   | DO    | Memory Card Write Protect Input. Connected<br>to Memory Card Socket. Optional.                         |

| CARD_CD#  | 13          | 7   | DI    | Memory Card Detect Input. Connected to<br>Memory Card Socket. Optional.                                |

| RSVD3     | 12          | _   |       | Reserved Pin 3. Do not connect.                                                                        |

| RSVD4     | 11          | _   |       | Reserved Pin 4. Do not connect.                                                                        |

| RSVD5     | 7           | _   |       | Reserved Pin 5. Do not connect.                                                                        |

| RSVD6     | 8           | _   |       | Reserved Pin 6. Do not connect.                                                                        |

| RSVD7     | 9           | _   |       | Reserved Pin 7. Do not connect.                                                                        |

| RSVD8     | 10          | _   |       | Reserved Pin 8. Do not connect.                                                                        |

-

-

-

-

-

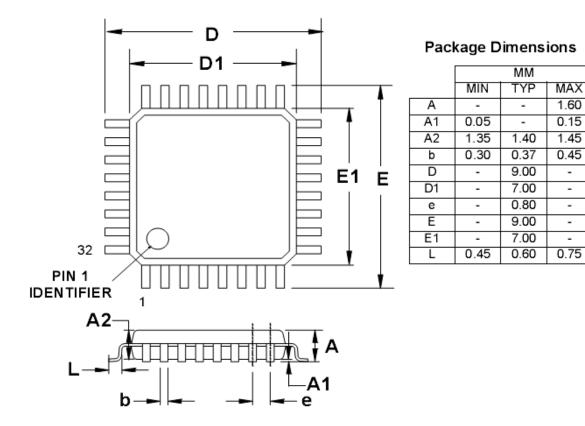

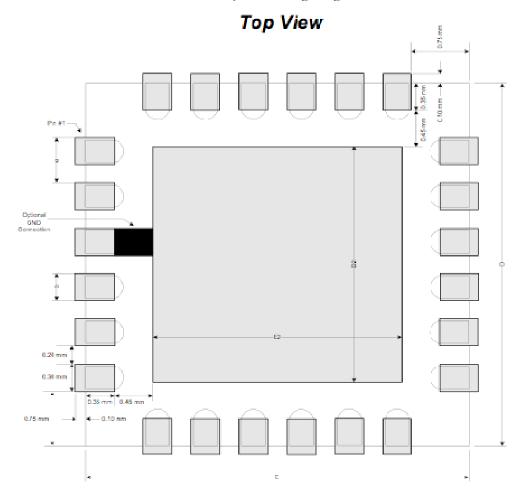

Table 4-2: QFP Package Dimensions

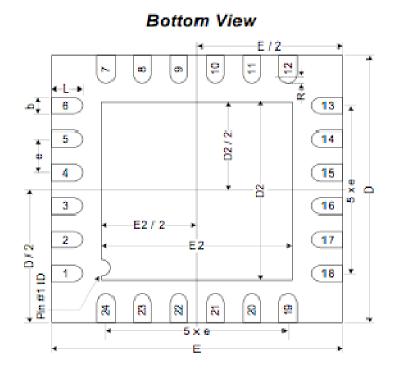

Table 4-3: QFN Package Dimensions

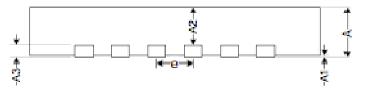

Side View

|    |      | MM   |      |

|----|------|------|------|

|    | MIN  | ТҮР  | MAX  |

| Α  | 0.70 | 0.75 | 0.80 |

| A1 | 0.00 | 0.02 | 0.05 |

| A2 |      | 0.50 |      |

| A3 | _    | 0.25 |      |

| b  | 0.18 | 0.25 | 0.30 |

| D  |      | 4.00 |      |

| D2 | 2.50 | 2.60 | 2.70 |

| Е  | _    | 4.00 |      |

| E2 | 2.50 | 2.60 | 2.70 |

| e  | _    | 0.50 |      |

| L  | 0.35 | 0.40 | 0.45 |

| Ν  |      | 24   |      |

| ND |      | 6    |      |

| NE |      | 6    |      |

| R  | 0.09 |      |      |

### 5. Reset & Power-Up Configuration

The RESET# pin is an open-drain bidirectional pin that provides input for an external reset and an output to signal an internal reset. The internal resets consist of a power-on reset and a power-fail reset. The three reset sources are connected in a "wired OR" configuration.

#### 5.1. **Power-on Reset**

During power-up, the RESET# line will be held low until a short delay after VDD settles above VRST.

Note that if the VDD Ramp Time (see Table 3-2) is greater than 1ms then an external voltage supervisor must be used to prevent possible corruption of the firmware memory. In the event the firmware memory becomes corrupt, the CD17B10 may become unstable/unusable and it may no longer be possible to perform In System Updates.

#### 5.2. **Power-fail Reset**

Whenever VDD drops below VRST, whether due to a power transition or power irregularity, the CD17B10 will go into reset and drive the RESET# line low until a short delay after VDD settles above VRST.

#### 5.3. **External Reset**

The RESET# signal pin can be driven low to reset the CD17B10. If the external driving signal has a high state, then a series resistor should be used to prevent a short condition when the RESET# line outputs a low state. See Table 3-2 for the minimum time that RESET# must be held low.

#### 5.4. Pin States During Reset

During any reset event and while the RESET# line is low, the CD17B10's remaining signal pins are placed in a high impedance state with weak pull-up resistors.

#### 5.5. **Reset Wake-up**

If at any time the CD17B10 is placed in Shutdown to minimize power consumption, it can only be woken-up by a reset event.

### 6. Communication Ports

#### 6.1. Host Ports

There are three physical communication ports that can be used to interface to the CD17B10:

| <b>Physical Port</b>   | Bootloader 1.x | Firmware 1.x  | Firmware 2.x |

|------------------------|----------------|---------------|--------------|

| UART                   | Supported      | Supported     | Supported    |

| SPI                    | Not Supported  | Supported     | Supported    |

| I <sup>2</sup> C/SMBus | Not Supported  | Not Supported | Planned      |

Table 6-1: Physical Communication Ports

Only one Host Port can be used at a time and is selected at reset using the MODE0 and MODE1 pins. The state of the MODEx pins must be maintained during operation of the CD17B10. If a change is required during operation, make sure the CD17B10 has completed any pending operations, all files are closed, then change the MODEx pins and generate a reset event (see Section 5).

# <u>A change in either or both of the MODEx pins at any other time may lead to unpredictable</u> results including the possibility of lost application data.

Use the following table to select the desired Host Port:

| MODE0    | MODE1    | Host Port                        |

|----------|----------|----------------------------------|

| Open/VCC | Open/VCC | UART                             |

| Open/VCC | GND      | SPI (slave)                      |

| GND      | Open/VCC | Start Bootloader                 |

| GND      | GND      | I <sup>2</sup> C/SMBus address 0 |

Table 6-2: Communication Port Selection via MODEx Pins

#### 6.2. **UART**

The UART, or Universal Asynchronous Receiver & Transmitter, provides asynchronous digital serial communications with the host. The UART physical interface consists of the following signal pins:

- UART\_RX : Commands & data sent from host to the DOSonCHIP device.

- UART\_TX : Commands & data sent from the DOSonCHIP device to the host.

- UART\_CTS : Handshake signal from the host to the DOSonCHIP device. This signal is set to logical 1 (high) by the host to prevent the DOSonCHIP device from sending bytes to the host. This signal is optional for Firmware 2.x and if not used it must be tied to ground (low). This signal should be used by the Bootloader when updating firmware.

- UART\_RTS : Handshake signal from the DOSonCHIP device to the host. It is set to logical 0 (low) when the DOSonCHIP device is ready to accept data from the host. This signal is optional for Firmware 2.x. This signal should be used by the Bootloader when updating firmware.

#### **Baud Rate**

The baud rate is selected after the device comes out of reset and the UART or Bootloader is selected via the MODEx pins. The DOSonCHIP device baud rate is set using autobaud detection. 2 consecutive carriage returns (<CR>) are required to set the baud rate. The first carriage return sets the baud rate and the second carriage return is used to confirm that the baud rate is correct. The DOSonCHIP device will wait until two consecutive error free carriage return's are received at the same baud rate before sending the ready prompt. Please see the DOSonCHIP host source code for UART baud rate initialization.

The allowable baud rates are:

- 1200

- 2400

- 9600

- 28800

- 38400

- 57600

- 115200

- 230400

#### Figure 6-1: Application Circuit with UART interface and Real Time Clock

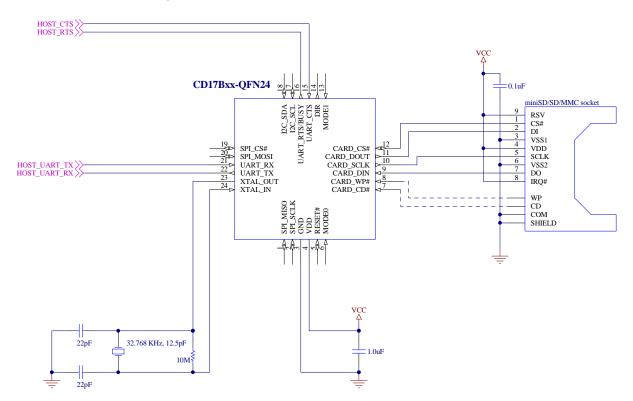

#### 6.3. **SPI**

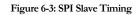

The SPI, or Serial Peripheral Interface, provides slave synchronous serial communications with the host. The SPI physical interface consists of the following signal pins:

- SPI\_MOSI : Commands & data sent from host to the DOSonCHIP device.

- SPI\_MISO : Commands & data sent from the DOSonCHIP device to the host.

- SPI\_CLK : Synchronous clock signal from host.

- SPI\_CS# : SPI port select signal from host. When this set to logical 1 (high), the SPI port will be disabled and SPI\_MISO will be placed in a high impedence state. When there is a transition from logical 1 (high) to logical 0 (low), it resets the DOSonCHIP bit counter; therefore, it should not be tied to logical 0 (low) as a default since noise on the SPI\_CLK line could offset the DOSonCHIP bit counter for all subsequent byte transfers.

- BUSY : Handshake from the DOSonCHIP device to the host. It is set to logical 0 (low) when the DOSonCHIP is ready to accept data from the host. This signal is optional for Firmware 2.x.

- DIR : Firmware 1.x only: data direction indicator line from the DOSonCHIP device to the host. It is set to logical 1 (high) to indicate the DOSonCHIP device is in a mode to accept data from the host. It is set at logical 0 (low) to indicate the DOSonCHIP device is in a mode to send data to the host. It is not used for Firmware 2.x.

#### Figure 6-2: Application Circuit with SPI interface (without Real Time Clock)

| Parameter        | Description                                                   | Min                                     | Max                                     | Units |

|------------------|---------------------------------------------------------------|-----------------------------------------|-----------------------------------------|-------|

| F <sub>CK</sub>  | SPI_CLK frequency                                             |                                         |                                         |       |

|                  | Firmware = 1.x                                                | 0                                       | 1.5                                     | MHz   |

|                  | Firmware = 2.x                                                | 0                                       | 2.4                                     |       |

| Т <sub>ск</sub>  | SPI_SCLK period                                               | $1/F_{CK}$                              | _                                       | ns    |

| T <sub>SE</sub>  | SPI_CS# Falling to First SPI_SCLK Edge                        | $2 \mathrm{x} \mathrm{T}_{\mathrm{CK}}$ | _                                       | ns    |

| T <sub>SD</sub>  | Last SPI_SCLK Edge to SPI_CS# Rising                          | $2 \mathrm{x} \mathrm{T}_{\mathrm{CK}}$ | _                                       | ns    |

| T <sub>SEZ</sub> | SPI_CS# Falling to SPI_MISO Valid                             | _                                       | 4 x T <sub>CK</sub>                     | ns    |

| T <sub>SDZ</sub> | SPI_CS# Rising to SPI_MISO High-Z                             | _                                       | $4 \mathrm{x} \mathrm{T}_{\mathrm{CK}}$ | ns    |

| Т <sub>скн</sub> | SPI_SCLK High Time                                            | 5 x T <sub>ck</sub>                     | _                                       | ns    |

| T <sub>CKL</sub> | SPI_SCLK Low Time                                             | 5 x T <sub>ck</sub>                     | _                                       | ns    |

| T <sub>SIS</sub> | SPI_MOSI Valid to SPI_SCLK Sample Edge                        | 2 x T <sub>CK</sub>                     | _                                       | ns    |

| T <sub>SIH</sub> | SPI_SCLK Sample Edge to SPI_MOSI Change                       | 2 x T <sub>CK</sub>                     | _                                       | ns    |

| T <sub>SOH</sub> | SPI_SCLK Shift Edge to SPI-MISO Change                        | _                                       | 4 x T <sub>CK</sub>                     | ns    |

| T <sub>SLH</sub> | Last SPI_SCLK Edge to SPI-MISO Change<br>(Clock Phase 1 only) | 6 x T <sub>ck</sub>                     | $8 \ge T_{CK}$                          | ns    |

Table 6-3: SPI Timing Parameter Table

#### 6.4. I<sup>2</sup>C/SMBus<sup>†</sup>

The I<sup>2</sup>C/SMBus provides synchronous serial communications with the host. It is compatible with the I<sup>2</sup>C serial bus and compliant with System Management Bus Specification, version 1.1. It functions in slave mode only (host is master). The I<sup>2</sup>C/SMBus physical interface consists of the following signal pins:

- I2C\_SDA : bidirectional slave port data line between host & DOSonCHIP device

- I2C\_SCL : bidirectional slave port clock line between host & DOSonCHIP device

The maximum clock speed is 2.4MHz.

The maximum rise and fall times must not exceed 300ns and 1000ns, respectively.

DOSonCHIP may temporarily hold the I2C\_SCL line low to extend the clock low period (per I2C and SMBus specifications). This depends upon the firmware and host clock speed.

### 7. Real Time Clock (RTC)

The Real Time Clock is an optional feature that provides the current date & time.

#### 7.1. Hardware Configuration

The RTC requires a 32.768 KHz, 50% duty cycle clock to function. This can be provided with a common watch crystal.

#### 7.1.1. External Crystal

Connect a tuning-fork crystal of 32.768 KHz with a recommended load capacitance of 12.5 pF as shown in Figure X.X. The total value of the capacitors and the stray capacitance of the XTAL pins should equal 25 pF. With a stray capacitance of 3 pF per pin, the 22 pF capacitors yield an equivalent capacitance of 12.5 pF across the crystal.

#### 7.1.2. No Clock/Disable RTC

If the RTC function is not needed, then either leave XTAL\_IN and XTAL\_OUT unconnected or connect the XTAL\_IN pin to GND and leave the XTAL\_OUT pin unconnected.

#### 7.2. Setting the Date & Time

When the RTC is disabled, the set time & date will remain static. This is useful for time stamping files with a specific date & time.

See the DOSonCHIP host source code for date and time commands.

#### 7.3. **Resetting of the Date & Time**

The set date and time will be reset if either of the following conditions occur:

- The CD17B10 is placed into Shutdown mode (via host command), or

- The CD17B10 is reset.

### 8. In-System Updates

The DOSonCHIP device can be updated with new firmware.

Firmware updating takes place over the UART interface using Ward Christensen's 1977 public domain XModem transfer protocol as documented in: [1] "XModem / YModem Protocol Reference" by Chuck Forsberg [1988-10-14]

```

[2] http://www.commonsoftinc.com/Babylon_Cpp/Documentation/Res/KRefFrame.htm

```

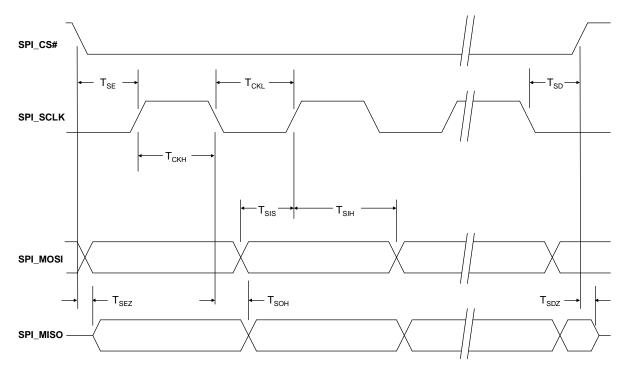

The following procedure uses Windows XP HyperTerminal to upload new firmware from 1.x to 2.x (and uses hardware handshaking). Follow similar guidelines for additional firmware updates:

#### 8.1. Windows HyperTerminal Setup

- 1. Launch HyperTerminal on the PC (Start>All Programs>Accessories<Communications>HyperTerminal).

- 2. At the "New Connection" prompt, choose a profile name for this connection:

| Connection Description 🛛 ? 🔀                        |

|-----------------------------------------------------|

| New Connection                                      |

| Enter a name and choose an icon for the connection: |

| Name:                                               |

| DOSonCHIP                                           |

| <u>l</u> con:                                       |

|                                                     |

| OK Cancel                                           |

3. Choose your RS-232 serial connection COM port at the next prompt:

| Connect To              |                                         |  |

|-------------------------|-----------------------------------------|--|

|                         |                                         |  |

| Enter details for       | the phone number that you want to dial: |  |

| <u>C</u> ountry/region: | United States (1)                       |  |

| Ar <u>e</u> a code:     | 847                                     |  |

| <u>P</u> hone number:   |                                         |  |

| Co <u>n</u> nect using: | СОМ2 🖌                                  |  |

|                         | OK Cancel                               |  |

4. At the next prompt, choose the serial port speed (see section 6.2 for allowable serial speeds), and choose the settings as shown:

| COM1 Properties          |          |               | ?×    |

|--------------------------|----------|---------------|-------|

| Port Settings            |          |               |       |

|                          |          |               |       |

| <u>B</u> its per second: | 115200   | ~             |       |

| Data bits:               | 8        |               |       |

|                          | 0        | v             |       |

| Parity:                  | None     | *             |       |

| <u>S</u> top bits:       | 1        | *             |       |

| <u>F</u> low control:    | Hardwara |               |       |

| <u>r</u> iow control.    | naiuwaie | •             |       |

|                          |          | Restore Defau | ults  |

|                          |          |               |       |

|                          | Can      | cel 🧾         | Apply |

5. On the menu bar, select "File>Properties" and click on the "Settings" tab and select the "ASCII Setup..." button. Then choose the settings as shown:

| ASCII Setup 🛛 🖓 🔀                                                                                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------|

| ASCII Sending   Send line ends with line feeds   Echo typed characters locally                                                         |

| Line delay: 0 milliseconds.                                                                                                            |

| ASCII Receiving   Append line feeds to incoming line ends   Eorce incoming data to 7-bit ASCII   Wrap lines that exceed terminal width |

| DK Cancel                                                                                                                              |

Make sure you press "OK" for both the "ASCII Setup" prompt AND the previous prompt for the settings to take effect.

6. On the PC's keyboard, press the "Enter/Return" button a minimum of two consecutive times to communicate and set the serial baud rate with on the CD17B10. You should now see the following prompt ">" from the CD17B10 (firmware 1.x):

7. Continue to the next section (File Transfer).

#### 8.2. File Transfer

- 1. There are 2 ways to initiate the Bootloader

- Set appropriate pins and reset the device (see Section 6.1), or

- Use the DOSonCHIP command.

- 2. Enter two carriage return's (press the Enter/Return key twice) to complete the CD17B10's autobaud detection. There should be a new "\$" symbol being shown about every second.

| 👋 DOSonCHIP - Hype    | erTerminal                                  |                    |

|-----------------------|---------------------------------------------|--------------------|

| File Edit View Call T | Transfer Help                               |                    |

| D 🚅 💿 🔏 🗈             | 🖰 🖆                                         |                    |

|                       |                                             | 1                  |

| >b<br>\$\$\$\$\$      |                                             |                    |

|                       |                                             |                    |

| Connected 0:00:14     | Auto detect 115200 8-N-1 SCROLL CAPS NUM Ca | pture Print echo 🥂 |

3. Select Transfer>Send File... on the Menu Bar and at the Send File prompt, select the firmware upgrade file (.ROM file), select the Xmodem protocol and press the "Send" button

| Send File         |                            | ? 🗙    |

|-------------------|----------------------------|--------|

| Folder: C:\UPGRA  | DE                         |        |

| <u>F</u> ilename: |                            |        |

| C:\UPGRADE\01     | 01.ROM                     | Browse |

| <u>P</u> rotocol: |                            |        |

| Xmodem            |                            | *      |

| -                 | <u>S</u> end <u>C</u> lose | Cancel |

4. The "Xmodem file send" progress display should show the uploading process

| Xmodem      | file send for DOSonCHIP         |

|-------------|---------------------------------|

| Sending:    | C:\UPGRADE\0101.ROM             |

| Packet:     | 17 Error checking: Checksum     |

| Retries:    | 0 Total retries: 0              |

| Last error: |                                 |

| File:       | 2K of 15K                       |

| Elapsed:    | 00:00:01 Remaining: Throughput: |

|             | Cancel                          |

5. After the file transfer completes and there are no errors, the new firmware will be executed. Enter two <CR>'s (press the Enter key twice ) to complete the CD17B10's autobaud detection.

# 9. Ordering Information

| Part Number | Supply Voltage | Temperature<br>Range | Package | Packing |

|-------------|----------------|----------------------|---------|---------|

| CD17B10-QFP | 2.7V to 3.3V   | Industrial           | QFP32   | Bulk    |

| CD17B10-QFN | 2.7V to 3.3V   | Industrial           | QFN24   | Bulk    |

- Industrial Temperature Range: -40 to +85 °C

- Tape & Reel packing upon request with volume minimums

## **10. Document Change List**

| Revision | Date       | Comments                                                       |

|----------|------------|----------------------------------------------------------------|

| 0.8      | 4/1/2006   | Initial Distribution.                                          |

| 1.0      | 3/14/2008  | Changed title & added firmware support table (6.1).            |

|          |            | Fixed error (6.2).                                             |

|          |            | Updated SPI timing parameters (6.3).                           |

|          |            | Updated spec (6.4).                                            |

|          |            | Added RTC date & time clock reset (7.3).                       |

|          |            | Added reference to User Guide (8).                             |

|          |            | Updated schematics.                                            |

|          |            | Updated table & figure references.                             |

|          |            | Updated company contact information.                           |

|          |            | Removed "Preliminary" status.                                  |

|          |            | Updated copyright.                                             |

| 1.1      | 4/19/2008  | Updated Table 3-2 formatting.                                  |

|          |            | Updated reference to Table 3-2 (5.1 & 5.3).                    |

|          |            | Updated 5.1.                                                   |

| 2.0      | 10/31/2008 | Changed chip reference from CD17Bxx to CD17B10.                |

|          |            | Updated Document for Firmware 2.x.                             |

|          |            | Updated reference for SDHC cards.                              |

|          |            | Added Table 4-2 (QFP package dimensions).                      |

|          |            | Added Table 4-3 (QFN package dimensions).                      |

|          |            | Added Table 4-4 (QFN landing diagram).                         |

|          |            | Updated UART & SPI signal pin definitions.                     |

|          |            | Added baud rate description to UART definition.                |

|          |            | Replaced reference to DOSonCHIP User Guide with DOSonCHIP host |

|          |            | source code.                                                   |

|          |            | Added MODEx for Bootloader.                                    |

|          |            | Updated Packing Order information.                             |

|          |            | Updated In-System Updates.                                     |

|          |            | Updated Contact Information.                                   |

### **11. Contact Information**

Wearable Inc. 3825 Charles Drive Northbrook, Illinois 60062 United States of America Email: support@dosonchip.com Website: dosonchip.com

<sup>†</sup>Planned feature (I<sup>2</sup>C/SMBbus compatibility) not currently available.

The information in this document is believed to be accurate in all respects at the time of publication but is subject to change without notice. Wearable Inc. assumes no responsibility for errors and omissions, and disclaims responsibility for any consequences resulting from the use of information included herein. Additionally, Wearable Inc. assumes no responsibility for the functioning of undescribed features or parameters. Wearable Inc. reserves the right to make changes without further notice. Wearable Inc. makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Wearable Inc. assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. Wearable Inc. products are not designed, intended, or authorized for use in applications intended to support or sustain life, or for any other application in which the failure of the Wearable Inc. products for any such unintended or unauthorized application, Buyer shall indemnify and hold Wearable Inc. harmless against all claims and damages.

DOSonCHIP<sup>™</sup> is a trademark of Wearable Inc.

Other products or brand names mentioned herein are trademarks or registered trademarks of their respective holders.