## 1/4 VGA Cholesteric Display Module with SPI<sup>™</sup>-Compatible Interface

### **Product Features**

#### **Display Module:**

- 320 Columns × 240 Rows

- Active Frame: 2 Rows and 2 Columns

- 72 dpi (pixels per inch)

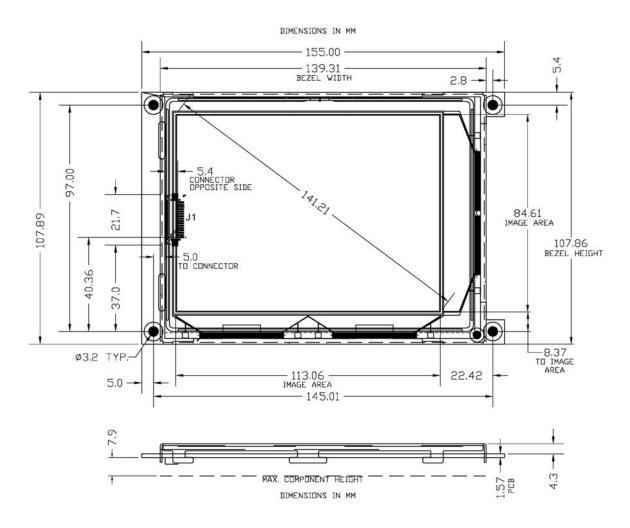

- Approximate Size: 155 x 108 x 14 mm

- Four Standard Colors

- Integrated LCD Bias Supply

#### Embedded Controller:

- Serial Peripheral Interface (SPI) Compatible

- 250 kbps Image Download

- 32 KB of Image Memory

- "No Power" Image Retention

- 3.3V Logic Supply

- 4.0V 9.0V Power Supply

- Viewing Cone Comparable to Paper

- Low Profile Modular Design

- Available with Optional Bezel

- 10 µA Sleep Current

- Full or Partial Screen Update Ability

| Туріс                                                                                                                | al Applications                                                                                                           |

|----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Battery Powered Portable Devices</li> <li>Machine Interface</li> <li>Inventory Tracking Displays</li> </ul> | <ul> <li>Instrumentation Displays</li> <li>Remote Control Display Applications</li> <li>Point of Sale Displays</li> </ul> |

| Kent Displays, Inc.<br>343 Portage Boulevard<br>Kent, OH 44240 USA                                                   | Telephone:330.673.8784Fax:330.673.4408Email:sales@kentdisplays.comWebsite:www.kentdisplays.com                            |

$SPI^{TM}$  is a trademark of Motorola Inc.

| $\mathbf{K}$ | FN |   | DISPLAYS     |

|--------------|----|---|--------------|

| 17           |    | T | INCORPORATED |

# 320×240×5.7 SPI

### **Specification Summary**

| Parameter                      | Description                                                                           |

|--------------------------------|---------------------------------------------------------------------------------------|

| Display Type                   | Reflective Cholesteric LCD                                                            |

| Format                         | 320 Columns × 240 Rows (318 x 238 Minus the Active Frame)                             |

| Resolution                     | 72 dots per inch,<br>0.36 mm between pixel centerlines (both horizontal and vertical) |

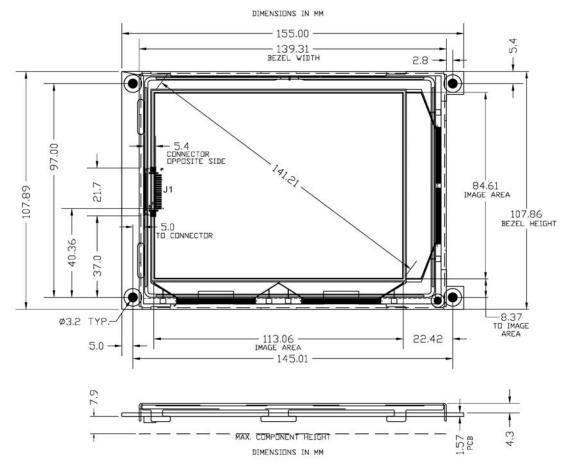

| Image Area                     | 113.06 mm × 84.61 mm (Dimensions do not include active frame.)                        |

| Display Module Weight          | 105 grams (Weight is 150 grams with optional bezel.)                                  |

| Operating Temperature<br>Range | 0°C to +60°C                                                                          |

| Storage Temperature Range      | -30°C to +80°C                                                                        |

| Full Image Update Rate         | 1.85 sec @ 25°C                                                                       |

(Shown with Optional Bezel)

# 320×240×5.7 SPI

### Contents

| 1  |                  | Ψ                                      |    |

|----|------------------|----------------------------------------|----|

| 2  |                  | liagram                                |    |

| 3  |                  | al Interface                           |    |

| -  |                  |                                        |    |

| -  |                  | Summary                                |    |

| 3. |                  | Functions                              |    |

|    | 3.3.1            | Logic Interface                        |    |

| 4  | 3.3.2            | Power Supply                           |    |

| -  |                  | ng Principles<br>ability               |    |

| 4. |                  | ial Interface                          |    |

| 4. |                  | ver On and Reset                       |    |

| 4. | .3 FUV<br>1 Elou | ctronic Erase (Pressure Point Removal) | 5  |

| 4  |                  | ve Frame                               |    |

|    |                  | ge Data                                |    |

| 5  |                  | cations                                |    |

|    |                  | neral                                  |    |

|    |                  | ctrical                                |    |

| 0. | 5.2.1            | Update Cycle Power Profiles            |    |

|    | 5.2.2            | Update Cycle Temperature Performance   |    |

| 5  |                  | ical                                   |    |

|    |                  | chanical                               |    |

|    |                  | ing                                    |    |

|    |                  | ion Set                                |    |

|    |                  | erview                                 |    |

| -  |                  | nory Access Commands                   |    |

|    | 6.2.1            | WRITE                                  |    |

|    | 6.2.2            | FILL                                   |    |

|    | 6.2.3            | READ                                   |    |

|    | 6.2.4            | CLEAR BITS                             |    |

|    | 6.2.5            | SET BITS                               |    |

|    | 6.2.6            | XOR BITS                               |    |

| 6. | .3 Disj          | play Update Commands                   |    |

|    | 6.3.1            | CLR_DISP_BRT                           |    |

|    | 6.3.2            | CLR DISP BRT IB                        |    |

|    | 6.3.3            | CLR_DISP_DRK                           | 15 |

|    | 6.3.4            | CLR DISP DRK IB                        |    |

|    | 6.3.5            | CLR SECT BRT.                          | 16 |

|    | 6.3.6            | CLR_SECT_BRT_IB                        | 16 |

|    | 6.3.7            | CLR_SECT_DRK                           | 16 |

|    | 6.3.8            | CLR_SECT_DRK_IB                        | 17 |

|    | 6.3.9            | DISP_FULLSCRN                          | 17 |

|    | 6.3.10           | DISP_PARTSCRN                          | 17 |

| 6. | .4 Sys           | tem Control Commands                   | 17 |

|    | 6.4.1            | SLEEP                                  | 17 |

|    | 6.4.2            | RESET                                  | 18 |

|    | 6.4.3            | GET_FW_VERSION                         |    |

|    | 6.4.4            | SET_CONTRAST                           |    |

|    | 6.4.5            | ELEC_ERASE                             |    |

| 7  |                  | I Heater                               |    |

|    |                  | R_DISABLE                              |    |

|    |                  | R_ENABLE                               |    |

|    |                  | R_SET_TEMP                             |    |

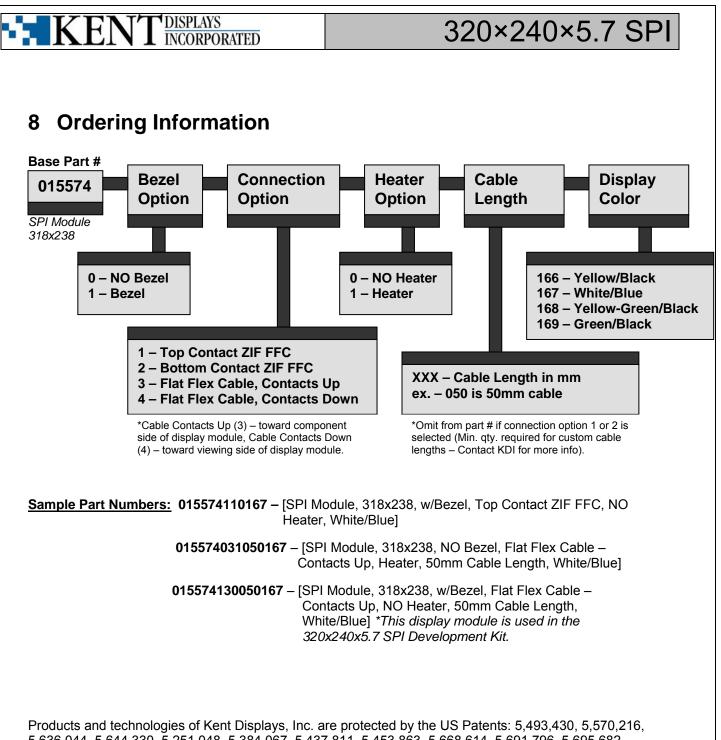

| 8  | Orderin          | g Information                          | 21 |

i

# 320×240×5.7 SPI

### 1 Overview

The 320x240 (1/4 VGA) ChLCD is a general-purpose graphic display module ideally suited for battery powered portable devices and display applications that require superior optical performance including wide viewing angle and sunlight readability. The display is a reflective cholesteric liquid crystal display (ChLCD) that takes full advantage of the technology's unique "No Power" image retention attribute. The embedded display controller generates the unique ChLCD drive waveforms and provides automatic temperature compensation. The SPI-compatible interface to the embedded controller simplifies system integration using a minimal number of I/O resources and controls all display operations, from downloading image data to triggering display updates. Bistable, sunlight readable, and easy to integrate, the 320x240 (1/4 VGA) is truly a unique LCD display solution.

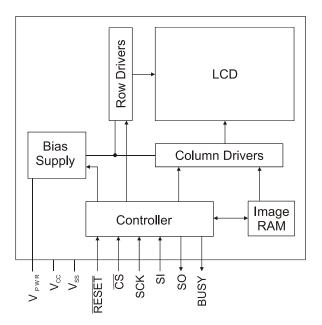

### 2 Block Diagram

### 3 Electrical Interface

### 3.1 Header

Electrical connection to the display module is made through the 16-contacts located at J1 (see section 5.4). Connection options include a 1mm pitch ZIF flat flex connector (FFC – with top or bottom contacts) soldered to the printed circuit board at J1, or a 50mm flat flexible cable soldered at J1 (with the cable contacts at the opposite end facing up – toward the component side of the display module, or down – toward the viewing side of the display module). Custom cable lengths are available upon request. Minimum quantities may apply for custom configurations.

# 320×240×5.7 SPI

### 3.2 Pin Summary

| Name             | Number    | Туре   | Description                                   |

|------------------|-----------|--------|-----------------------------------------------|

| RESET            | 1         | Input  | Reset (Optional Use).                         |

| BUSY             | 2         | Output | Display Busy Status Indicator (Optional Use). |

| V <sub>SS</sub>  | 3,8,12,14 | Supply | Ground.                                       |

| SCK              | 4         | Input  | Serial Data Clock.                            |

| SO               | 5         | Output | Serial Data Output.                           |

| SI               | 6         | Input  | Serial Data Input.                            |

| ĊŚ               | 7         | Input  | Chip Select.                                  |

| V <sub>CC</sub>  | 9         | Supply | Logic Supply (3.3V).                          |

| V <sub>PWR</sub> | 10,11,13  | Supply | Power Supply (4.0V – 9.0V).                   |

| NC               | 15,16     |        | No Connection.                                |

### 3.3 Pin Functions

### 3.3.1 Logic Interface

**SERIAL INPUT (SI):** The SI pin is used to shift commands and image data into the display module. Input is only accepted when the display is selected ( $\overline{CS}$  is low).

**SERIAL OUTPUT (SO):** The SO pin is used to shift data out of the display module. This pin is in a high-impedance state when the display is not selected ( $\overline{CS}$  is high).

**SERIAL CLOCK (SCK):** The SCK pin is used to clock data in and out of the display module. Input data is latched from SI on the falling edge of SCK and new data is output on SO on the rising edge of SCK.

**CHIP SELECT (CS):** The display module is selected when  $\overline{CS}$  is low. A high-to-low transition on  $\overline{CS}$  signifies the start of a new command packet. A low-to-high transition on  $\overline{CS}$  is required to end the commanded operation.

**RESET (RESET):** A low level on the RESET pin terminates any operation in progress and holds the controller in the reset state. The reset sequence executes when this pin is released to the high state. The display module enters the sleep mode upon termination of the reset sequence. There is no restriction on the RESET pin when powering on the display module. The RESET pin is internally pulled high, so this pin may be left unconnected.

**BUSY (BUSY):** The BUSY pin is high while the display module is processing a command and also during execution of the reset sequence. The BUSY pin must be low before the display may be selected ( $\overline{CS}$  set low). After receiving a command packet, the display module requires  $\overline{CS}$  to return high before the operation can complete and BUSY returns low. The display module is immediately ready for a new command packet when BUSY returns low. Module status may also be polled using the serial interface, which makes use of this pin optional.

### 3.3.2 Power Supply

**LOGIC SUPPLY (V<sub>cc</sub>):** The V<sub>cc</sub> pin provides regulated 3.3V power to the display module control logic, memory, and drivers.

**POWER SUPPLY (V**<sub>PWR</sub>): The V<sub>PWR</sub> pin provides DC power to the bias supply used to drive the ChLCD. For maximum efficiency, this supply may be unregulated. This pin draws zero current in sleep mode.

**GROUND** ( $V_{ss}$ ): The  $V_{ss}$  pin provides the return path for both  $V_{CC}$  and  $V_{PWR}$ .

# 320×240×5.7 SPI

### **4** Operating Principles

### 4.1 Bistability

The unique bistable property of ChLCD products means that an image placed on the display will remain indefinitely without the need for refreshing. This bistability has implications both for managing power consumption and for managing screen image content.

Display modules contain an onboard RAM into which image data is loaded using the SPI-compatible interface. Due to the bistability of the display, there is no continuous refresh and changes to the image data in the RAM do not automatically appear on the display. The displayed image only changes in response to the display update commands (see Section 6.3). The DISP\_FULLSCRN and DISP\_PARTSCRN commands are used, respectively, to update the entire display or a section of the display using image data stored in the RAM. The entire 32 KB RAM space is available to the application. The RAM is larger than required to hold a single full screen image and may be partitioned in any manner suitable to the application. Both update commands accept the starting address for the image data as an argument.

The display module contains the LCD bias supply that generates the 30 to 40 volts necessary to drive the display. This supply is normally on and drawing current from  $V_{PWR}$  when the display is idle. By leaving the bias supply on, the display can begin an update in a relatively short time ( $t_{HVCCHG}$ ). A longer time is required ( $t_{HVCON}$ ) to begin an update when the bias supply requires initialization. However, considerable power can be saved for infrequent display updates by using the sleep mode (see SLEEP, Section 6.4.1). The bias supply is disabled in sleep mode, with the result that the current drawn from  $V_{PWR}$  goes to zero. Note that the contents of the image RAM are preserved in sleep mode.

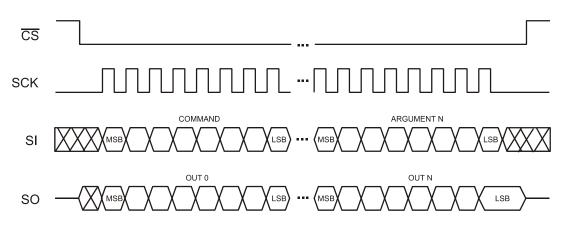

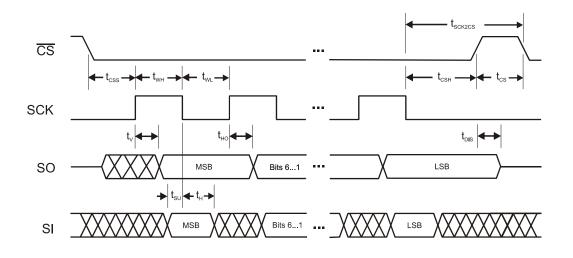

### 4.2 Serial Interface

The display module functions as a SPI slave device. The master selects the display for communication using the  $\overline{CS}$  line and provides the clock signal (SCK) used to clock data in and out of the display module. All new command packets to the display begin with a high-to-low transition on  $\overline{CS}$ . The  $\overline{CS}$  line must remain low until the command and all arguments are clocked into the display, at which time it is to return high. New data (commands or arguments) for the display are placed on SI on rising edges of SCK, and the display latches the data on the falling edge of SCK. The display places new output data on SO on rising edges of SCK for reading by the master on the falling edge. Thus, the display will output a byte of data on SO for every byte of data clocked in on SI. Transmission of each byte begins with the most significant bit (MSB) and ends with the least significant bit (LSB).

Figure 1 illustrates the basic interface timing for sending a command packet to the display module. The command is always the first byte clocked in following the high-to-low transition on  $\overline{CS}$ . The command arguments, numbered 1 to N, are clocked in next. Some commands have no arguments while others have many. The first byte output by the slave, numbered 0, clocks synchronously with the command byte. Slave output bytes 1 through N are clocked synchronously with the respective argument numbered 1 to N. See Section 5.5 for detailed timing information.

Figure 1: Basic Serial Interface Timing

Two alternative methods exist for determining the display module's readiness to accept new commands. The first method requires monitoring the BUSY signal (pin 2), while the second method requires using the serial interface to poll the display module's status register.

#### **BUSY Signal:**

Display modules output a BUSY signal (pin 2) that indicates the readiness of the display to accept new commands. A high on the BUSY pin indicates that the display is currently processing a previous command (or executing the reset sequence) and no new commands will be accepted. The master device must wait for the BUSY line to return low before asserting  $\overline{CS}$  low to send a new command packet. Once  $\overline{CS}$  is asserted low, the command and all of its arguments may be clocked in without regard to the BUSY line. Note that the  $\overline{CS}$  line must return high after the entire command is clocked in. The BUSY line will not return low again, freeing up the display to execute additional commands, until after  $\overline{CS}$  returns high.

#### Serial Polling:

The display status may alternatively be determined using the serial interface. This approach has the advantage of saving the I/O resource required by the BUSY line. However, the interface is more complex and the SPI port will be in use for longer durations. First, the commands are partitioned into those with fixed execution times and those with variable execution times. The variable execution time commands require special monitoring for completion. The fixed execution time commands require no special monitoring and permit the display module to be deselected ( $\overline{CS}$  high) immediately after the command packet is transmitted.

The procedure for variable execution time commands with serial polling is detailed as follows. The  $\overline{CS}$  line to the display module is asserted low and the command and arguments are clocked in. Following the command and arguments, additional dummy bytes are clocked in (with  $\overline{CS}$  remaining low). The display module's status register is output (on SO) with every byte. The high order bit of the status register indicates the busy status of the display module. This bit is a '1' while the display is busy, and a '0' when the operation is complete and the display is not busy. Note that the output pipeline of the display module requires three output bytes after the operation is complete for the not busy status to appear. The display may be deselected ( $\overline{CS}$  high) once the status byte containing the '0' busy bit is received.

Two additional signal timing constraints,  $t_{CS}$  and  $t_{SCK2CS}$ , are required for the serial polling method. These constraints are automatically satisfied when the BUSY signal is used. The first parameter,  $t_{CS}$ , is the minimum time that  $\overline{CS}$  must be high between any two command packets. The second parameter,  $t_{SCK2CS}$ , is the minimum time from the falling edge of SCK on the last bit in a command packet until the high-to-low transition on  $\overline{CS}$  that begins a new command packet. These two constraints must be satisfied for all command packets (both fixed and variable execution time commands).

# 320×240×5.7 SPI

### 4.3 Power On and Reset

The display module executes an internal reset sequence in response to hardware and software resets and also at power on. A hardware reset is triggered when the RESET pin returns high after being held low for a minimum of  $t_{RST}$ . Software resets are triggered by the RESET command (see Section 6.4.2). The BUSY pin may be monitored to determine when the reset sequence has completed and the display module is ready to accept new command packets. For applications where the BUSY line is not connected (serial polling of display module status is implemented), it is necessary to wait for a period of  $t_{RESET}$  after triggering the reset sequence before issuing new command packets to the display module. The display module is in the sleep mode upon completion of the reset sequence.

### 4.4 Electronic Erase (Pressure Point Removal)

Application of external pressure to the display module glass or PCB may produce visual non-uniformities as a result of liquid crystal flow. These non-uniformities, called pressure points, typically appear as bright spots. Some pressure points can be removed by updating the display using the Display Update Commands (see Section 6.3), but some pressure points that result from higher pressures cannot. In particular, the interpixel area cannot be driven to the dark state using the Display Update Commands.

The electronic erase command (see ELEC\_ERASE, Section 6.4.5) may be used to completely remove pressure points from the active area of the display. This command leaves all pixels in the bright state with the interpixel area in the dark state. This command is provided to assist OEM customers in assembling the display modules into their devices. An electronic erase command may be issued after final product assembly in order to clear any pressure points created in handling and mounting the displays. This command should only be used for the infrequent removal of pressure points, not for erasing the display during normal operation, as extensive use of this command may shorten the operating lifetime of the display.

### 4.5 Active Frame

The active (drivable) area of the display is slightly smaller than the glass substrates that form the display. The inactive portion of the glass should generally not be visible in the final product assembly as the electronic erase is unable to remove pressure points in this area. Display modules include an active frame that enables creation of a pressure-point free border around the image content area of the display. The active frame consists of a five-pixel wide border, which is controlled in the same manner as normal image data. Suitable framing should be used to partially overlap the active frame and mask off the inactive area. The optional bezel may be used for this purpose.

# **KENT**

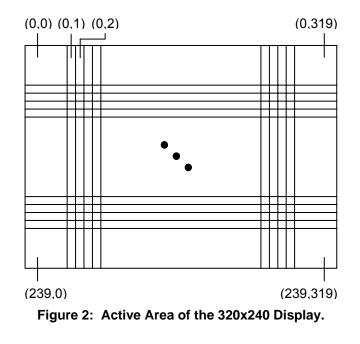

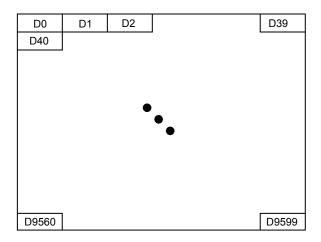

Figure 2 illustrates the row and column numbering as well as the active frame for the 320x240 display module. These modules have 320 columns, numbered 0 to 319, and 240 rows, numbered 0 to 239. Note that the first (0) and last (319) columns appear five pixels wide, while the first (0) and last (239) rows appear five pixels tall. Thus, image data destined for these locations is stretched in order to produce the active frame. Typically, image data is selected the same for all active frame locations in order to produce a solid border for the image. Once the active frame is taken into account, 318 columns and 238 rows are available for general image content.

### 4.6 Image Data

A full screen update of the 320x240 display module requires 9600 bytes (= 240 x 320 pixels x 1 bit/pixel x 1 byte / 8 bits) of image data. The first byte of data defines the leftmost 8 pixels in the top row. Successive bytes map to the next 8 pixels to the right. When the end of a row is reached, the next byte maps to the leftmost 8 pixels of the following row. A bright (on) pixel is a binary one, while a dark (off) pixel is a binary zero. The leftmost pixel encoded in a given byte corresponds to the most significant bit in the byte while the rightmost pixel corresponds to the least significant bit.

Figure 3 illustrates how the byte data maps to the display. The bytes are labeled D0 through D9599, with D0 being the first byte in the image buffer and D9599 the last. Note again that the active frame will cause the data encoded in the first (D0 – D39) and last (D9570 – D9599) rows to appear five pixels high on the display. Also, the single bit that encodes a column 0 pixel will appear five pixels wide as will the single bit that encodes a column 319 pixel.

Figure 3: 320x240 Display Screen Location to Image Data Mapping.

Partial screen updates (update a limited number of whole rows; all columns in the row), are also available. The mapping for partial screen updates is similar. However, less data is required (40 bytes times the number of rows to update). For partial screen updates, D0 maps to the upper left corner of the region to be updated rather than the upper left corner of the display.

### **KENT** INCORPORATED

# 320×240×5.7 SPI

### **5** Specifications

### 5.1 General

| Parameter                   | Description                                                      |

|-----------------------------|------------------------------------------------------------------|

| Display Type                | Reflective Cholesteric LCD                                       |

| Format                      | 320 Columns × 240 Rows (318 x 238 Minus the Active Frame)        |

| Resolution                  | 72 dots per inch,                                                |

|                             | 0.36 mm between pixel centerlines (both horizontal and vertical) |

| Image Area                  | 113.06 mm × 84.61 mm (Dimensions do not include active frame.)   |

| Display Module Weight       | 105 grams (Weight is 150 grams with optional bezel.)             |

| Operating Temperature Range | 0°C to +60°C                                                     |

| Storage Temperature Range   | -30°C to +80°C                                                   |

| Full Image Update Rate      | 1.85 sec @ 25°C (Ref. graph, 5.2.2)                              |

### 5.2 Electrical

| Parameter                                    | Minimum           | Typical              | Maximum | Units                |     |

|----------------------------------------------|-------------------|----------------------|---------|----------------------|-----|

| Logic Supply (V <sub>CC</sub> ) <sup>1</sup> |                   | 3.0                  | 3.3     | 3.6                  | VDC |

| Power Supply (V <sub>PWR</sub> )             |                   | 4.0                  | -       | 9.0                  | VDC |

| High Level Logic Output Voltage (            | V <sub>OH</sub> ) | V <sub>CC</sub> -0.6 | -       | V <sub>CC</sub>      | VDC |

| Low Level Logic Output Voltage (             | / <sub>OL</sub> ) | V <sub>SS</sub>      | -       | V <sub>SS</sub> +0.6 | VDC |

| High Level Logic Input Voltage (V            | н)                | 0.8xV <sub>CC</sub>  | -       | V <sub>CC</sub>      | VDC |

| Low Level Logic Input Voltage (VII           | )                 | V <sub>SS</sub>      | -       | V <sub>SS</sub> +0.6 | VDC |

| Average Operating Power                      | V <sub>CC</sub>   | -                    | 7       | -                    | mW  |

| @25°C (while driving image) <sup>2</sup>     | V <sub>PWR</sub>  | -                    | 150     | -                    | mW  |

| Average Operating Power                      | V <sub>CC</sub>   | -                    | 7       | -                    | mW  |

| @60°C (while driving image) <sup>2</sup>     | V <sub>PWR</sub>  | -                    | 234     | -                    | mW  |

| Standby Current <sup>2</sup>                 | V <sub>CC</sub>   | -                    | 156     | -                    | μA  |

|                                              | V <sub>PWR</sub>  | -                    | 13      | -                    | mA  |

| Sleep Current <sup>2</sup>                   | V <sub>CC</sub>   | -                    | 10      | -                    | μA  |

|                                              | V <sub>PWR</sub>  | -                    | 0       | 1                    | μA  |

<sup>2</sup> Test Conditions:  $V_{CC}$  = 3.3V and  $V_{PWR}$  = 5.0V.

<sup>&</sup>lt;sup>1</sup> V<sub>CC</sub> must rise/fall with a slope  $\geq$  1V/ms. If this requirement can not be satisfied, the RESET pin must be asserted low while V<sub>CC</sub>  $\leq$  2.7V.

####

# 320×240×5.7 SPI

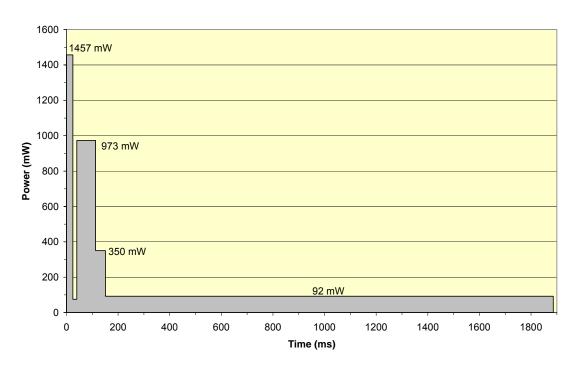

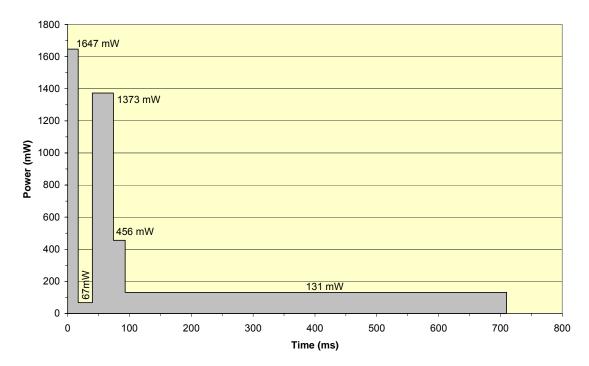

### 5.2.1 Update Cycle Power Profiles

320x240 SPI Display Module Update Cycle Power @25°C

#### 320x240 SPI Display Module Update Cycle Power @60°C

**Note:** Graphs above represent power required for a single full screen update. Initial power surge corresponds to capacitive loading in power supply circuit. Average power consumed during display update is 150 mW at 25°C and 234 mW at 60°C. Test Conditions:  $V_{CC} = 3.3V$  and  $V_{PWR} = 5.0V$ .

# 320×240×5.7 SPI

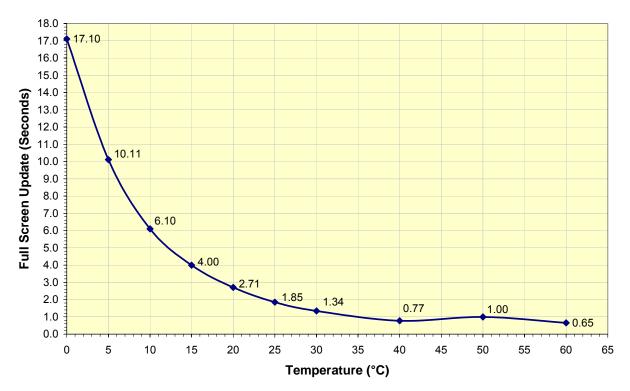

### 5.2.2 Update Cycle Temperature Performance

320x240 SPI Display Module Total Update Time

The chart above illustrates average computed full screen update times with respect to temperature for the 320×240 SPI display module (Blue/White). The update time is approximately 1.85 seconds at room temperature (25°C).

# **KENT**<u>INCORPORATED</u>

## 320×240×5.7 SPI

### 5.3 Optical

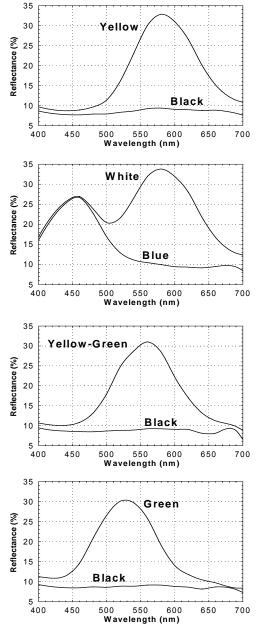

The above reflectance curves are from a single pixel. Actual reflectance will vary depending on display resolution, aperture ratio, and other factors.

The graphs to the left outline the spectral reflectance characteristics for a given display pixel when switched to either of the two possible stable states: reflective planar or transparent focal conic. The top line in each chart outlines the reflective characteristic of the planar state. The bottom line outlines the reflective characteristic of the transparent focal conic state. Graphs for the 4 standard color combinations are illustrated.

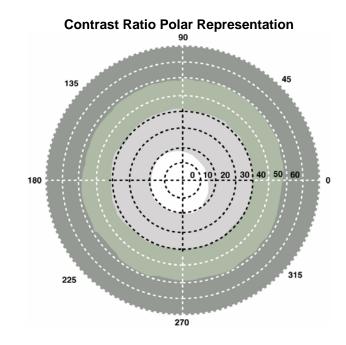

As illustrated in the polar graph above, all Kent Displays' ChLCD products have a 360-degree viewing cone. When measured normal to the plane of the display, the monochromatic contrast ratio is as high as 25:1 with a peak reflectivity approaching 35% of the incident light. The contrast ratio reduces as the viewing angle approaches the plane of the display but is still excellent at 11:1. Since no polarizers are used, display contrast reduces uniformly in all azimuthal directions when the viewing angle is increased.

# **KENT**<u>DISPLAYS</u> <u>INCORPORATED</u>

## 320×240×5.7 SPI

### 5.4 Mechanical

(Shown with Optional Bezel)

#### FRONT COVER REQUIREMENTS:

The following front cover requirements are necessary to insure image quality during the life of the 320×240 display module:

- 1. Cholesteric Liquid Crystal materials require protection from UV light. A UV blocking material with a minimum 98% cutoff at 380nm and lower spectral components is required.

- 2. The finished product design should incorporate a transparent cover such as acrylic, polycarbonate, etc., to protect the viewing area of the display. Place the protective cover as close to the display module as possible. The protective cover should be of sufficient thickness to resist flexing, or if flexed should not touch the surface of the display. Acrylite<sup>®</sup> OP-3 P-99 matte finish and Acrylite<sup>®</sup> OP-3 material without matte finish are examples of a recommended protective cover material.

Adding an anti-glare and/or anti-reflective surface film or finish (e.g. Acrylite<sup>®</sup> OP-3 P-99) to the viewing side of the protective cover may improve the optical performance in certain display applications and lighting conditions.

# **KENT**<u>DISPLAYS</u> <u>INCORPORATED</u>

### 5.5 Timing

| Symbol              | Parameter                       | Min.             | Max.             | Units |

|---------------------|---------------------------------|------------------|------------------|-------|

| f <sub>scк</sub>    | SCK Frequency                   | -                | 250              | kHz   |

| t <sub>wH</sub>     | SCK High Time                   | tbd <sup>1</sup> | -                | ns    |

| t <sub>wL</sub>     | SCK Low Time                    | tbd <sup>1</sup> | -                | ns    |

| t <sub>cs</sub>     | CS High Time                    | 40               | -                | μs    |

| t <sub>sck2cs</sub> | Last Data SCK to CS Low Time    | 60               | -                | μs    |

| t <sub>css</sub>    | CS Setup Time                   | tbd <sup>1</sup> | -                | ns    |

| t <sub>csH</sub>    | CS Hold time                    | tbd <sup>1</sup> | -                | ns    |

| t <sub>su</sub>     | Data In Setup Time              | tbd <sup>1</sup> | -                | ns    |

| t <sub>H</sub>      | Data In Hold Time               | tbd <sup>1</sup> | -                | ns    |

| t <sub>HO</sub>     | Output Hold Time                | -                | tbd <sup>1</sup> | ns    |

| t <sub>DIS</sub>    | Output Disable Time             | -                | tbd <sup>1</sup> | ns    |

| t <sub>v</sub>      | Output Valid                    | -                | tbd <sup>1</sup> | ns    |

| t <sub>RST</sub>    | RESET Pulse Width               | 2                | -                | μs    |

| t <sub>RESET</sub>  | Duration of Reset Sequence      | -                | 1                | S     |

| t <sub>HVCON</sub>  | Bias Supply Initialization Time | -                | 60               | ms    |

| t <sub>HVCCHG</sub> | Bias Supply Change Time         | -                | 17               | ms    |

<sup>1</sup> - Texas Instruments micro-controller (MSP430-F135) data pending.

# 320×240×5.7 SPI

### 6 Instruction Set

### 6.1 Overview

| _        |                              |                         |                                                    | De            | etails  |

|----------|------------------------------|-------------------------|----------------------------------------------------|---------------|---------|

| Function | Command                      | Command Hex Description | Description                                        | # of<br>Bytes | Section |

|          | WRITE                        | 00                      | Write byte data to RAM.                            | 4+            | 6.2.1   |

|          | FILL <sup>1</sup>            | 01                      | Fill RAM with single byte.                         | 6             | 6.2.2   |

| Memory   | READ                         | 04                      | Read byte data from RAM.                           | 6+            | 6.2.3   |

| wentory  | CLEAR_BITS                   | 08                      | Clear bits in RAM.                                 | 4             | 6.2.4   |

|          | SET_BITS                     | 09                      | Set bits in RAM.                                   | 4             | 6.2.5   |

|          | XOR_BITS                     | 0A                      | Exclusive-Or bits in RAM.                          | 4             | 6.2.6   |

|          | CLR_DISP_BRT <sup>1</sup>    | 10                      | Clear display bright.                              | 1             | 6.3.1   |

|          | CLR_DISP_BRT_IB <sup>1</sup> | 11                      | Clear display bright with inverted border.         | 1             | 6.3.2   |

|          | CLR_DISP_DRK <sup>1</sup>    | 12                      | Clear display dark.                                | 1             | 6.3.3   |

|          | CLR_DISP_DRK_IB <sup>1</sup> | 13                      | Clear display dark with inverted border.           | 1             | 6.3.4   |

| Display  | CLR_SECT_BRT <sup>1</sup>    | 14                      | Clear display section bright.                      | 5             | 6.3.5   |

| Display  | CLR_SECT_BRT_IB <sup>1</sup> | 15                      | Clear display section bright with inverted border. | 5             | 6.3.6   |

|          | CLR_SECT_DRK <sup>1</sup>    | 16                      | Clear display section dark.                        | 5             | 6.3.7   |

|          | CLR_SECT_DRK_IB <sup>1</sup> | 17                      | Clear display section dark with inverted border.   | 5             | 6.3.8   |

|          | DISP_FULLSCRN <sup>1</sup>   | 18                      | Update entire display.                             | 3             | 6.3.9   |

|          | DISP_PARTSCRN <sup>1</sup>   | 19                      | Update display section.                            | 7             | 6.3.10  |

|          | SLEEP                        | 20                      | Enter low-power sleep mode.                        | 1             | 6.4.1   |

|          | RESET <sup>2</sup>           | 24                      | Software reset.                                    | 1             | 6.4.2   |

| System   | GET_FW_VERSION               | 26                      | Get firmware version.                              | 36            | 6.4.3   |

|          | SET_CONTRAST                 | 27                      | Set display contrast.                              | 2             | 6.4.4   |

|          | ELEC_ERASE <sup>1</sup>      | 2A                      | Electronic erase (Clear pressure points).          | 1             | 6.4.5   |

<sup>1</sup> – Variable Execution Time Command

<sup>2</sup> – The RESET command requires an additional delay (t<sub>RESET</sub>) after being issued if the serial status polling method is used.

### 6.2 Memory Access Commands

The display module contains onboard image RAM that may be read from or written to using the memory access commands.

### 6.2.1 WRITE

This command provides byte-level write access to the display module's onboard image RAM. The command requires a minimum of 3 arguments.

| (CMD)  | 0x00:     | The command.                            |

|--------|-----------|-----------------------------------------|

| (ARG1) | ADDRESSH: | High byte of the target memory address. |

| (ARG2) | ADDRESSL: | Low byte of the target memory address.  |

| (ARG3) | DATA:     | The value to be written.                |

Data can be written to successive addresses by including more arguments. For instance, the optional argument ARG4 would contain the value to write to address  $\langle ARG1:ARG2 \rangle + 1$ . This feature permits the efficient transfer of an entire image to the display RAM. The low-to-high transition on  $\overline{CS}$  signals to the controller that the last byte of data has been written.

## 320×240×5.7 SPI

### 6.2.2 FILL

This command fills an entire region of the display module's onboard image RAM with a given value. The use of this command with a fill value of 0x00 or 0xFF is the recommended method of clearing an image buffer. The command has 5 arguments.

| (CMD)  | 0x01:       | The command.                                          |

|--------|-------------|-------------------------------------------------------|

| (ARG1) | STARTH:     | High byte of the first address in the fill region.    |

| (ARG2) | STARTL:     | Low byte of the first address in the fill region.     |

| (ARG3) | ENDH:       | High byte of the last address in the fill region.     |

| (ARG4) | ENDL:       | Low byte of the last address in the fill region.      |

| (ARG5) | FILL_VALUE: | Value to write to all memory locations in the region. |

This is a variable execution time command.

### 6.2.3 READ

This command provides byte-level read access to the display module's onboard image RAM. The command requires a minimum of 5 arguments.

| (CMD)  | 0x04:     | The command.                             |

|--------|-----------|------------------------------------------|

| (ARG1) | ADDRESSH  | High byte of the memory address to read. |

| (ARG2) | ADDRESSL: | Low byte of the memory address to read.  |

| (ARG3) | DUMMY1:   | Don't care.                              |

| (ARG4) | DUMMY2:   | Don't care.                              |

| (ARG5) | DUMMY3:   | Don't care.                              |

The display module will output (on SO) the contents of the memory location encoded in ARG1 and ARG2 (mem(<ARG1:ARG2>)) during receipt of ARG5. Additional dummy arguments may be used to obtain the contents of successive memory locations. For example, during optional dummy argument ARG6, the display module outputs mem(<ARG1:ARG2>+1). The low-to-high transition on  $\overline{CS}$  signals to the controller that the last byte of data has been read.

### 6.2.4 CLEAR\_BITS

This command provides the ability to clear (set to 0) individual bits in the display module's onboard image RAM. A bit mask is used to specify which bits at a given memory address should be cleared. A one in the mask indicates that the corresponding bit should be cleared, while a zero indicates that the corresponding bit should be left unaffected. The command has 3 arguments.

| (CMD)  | 0x08:     | The command.                               |

|--------|-----------|--------------------------------------------|

| (ARG1) | ADDRESSH: | High byte of the memory address to modify. |

| (ARG2) | ADDRESSL: | Low byte of the memory address to modify.  |

| (ARG3) | MASK:     | The bit mask.                              |

This command is useful for generating dark text or drawing with a dark pen directly to image RAM.

# 320×240×5.7 SPI

### 6.2.5 SET\_BITS

This command provides the ability to set (set to 1) individual bits in the display module's onboard image RAM. A bit mask is used to specify which bits at a given memory address should be set. A one in the mask indicates that the corresponding bit should be set, while a zero indicates that the corresponding bit should be left unaffected. The command has 3 arguments.

| (CMD)  | 0x09:                                      | The command.                              |

|--------|--------------------------------------------|-------------------------------------------|

| (ARG1) | High byte of the memory address to modify. |                                           |

| (ARG2) | ADDRESSL:                                  | Low byte of the memory address to modify. |

| (ARG3) | MASK:                                      | The bit mask.                             |

This command is useful for generating bright text or drawing with a bright pen directly to image RAM.

### 6.2.6 XOR\_BITS

This command provides the ability to toggle (exclusive-or) individual bits in the display module's onboard image RAM. A bit mask is used to specify which bits at a given memory address should be toggled. A one in the mask indicates that the corresponding bit should be toggled, while a zero indicates that the corresponding bit should be left unaffected. The command has 3 arguments.

| (CMD)  | 0x0A:     | The command.                               |

|--------|-----------|--------------------------------------------|

| (ARG1) | ADDRESSH: | High byte of the memory address to modify. |

| (ARG2) | ADDRESSL: | Low byte of the memory address to modify.  |

| (ARG3) | MASK:     | The bit mask.                              |

This command is useful for generating text or drawing directly to image RAM without regard to the background color.

### 6.3 Display Update Commands

The display update commands drive new image data to the display.

### 6.3.1 CLR\_DISP\_BRT

This command clears the entire display, including the active frame, to the bright state. There are no arguments.

(CMD) 0x10: The command.

This is a variable execution time command.

### 6.3.2 CLR\_DISP\_BRT\_IB

This command clears the entire display, less the active frame, to the bright state. The active frame is set to the dark state, i.e. the border is inverted. There are no arguments.

(CMD) 0x11: The command.

This is a variable execution time command.

### 6.3.3 CLR\_DISP\_DRK

This command clears the entire display, including the active frame, to the dark state. There are no arguments.

(CMD) 0x12: The command.

This is a variable execution time command.

# **KENT**<u>DISPLAYS</u> <u>INCORPORATED</u>

# 320×240×5.7 SPI

### 6.3.4 CLR\_DISP\_DRK\_IB

This command clears the entire display, less the active frame, to the dark state. The active frame is set to the bright state, i.e. the border is inverted. There are no arguments.

(CMD) 0x13: The command.

This is a variable execution time command.

### 6.3.5 CLR\_SECT\_BRT

This command clears a given section of the display to the bright state. The section is defined by the first and last rows (numbered 0 to 239). Any part of the active frame (left/right and top/bottom) in the defined section is also set to the bright state. The maximum number of rows that may be cleared using this command is 120. The command has 4 arguments.

| (CMD)  | 0x14:                                | The command.                        |

|--------|--------------------------------------|-------------------------------------|

| (ARG1) | High byte of the first row to clear. |                                     |

| (ARG2) | FIRSTL:                              | Low byte of the first row to clear  |

| (ARG3) | LASTH:                               | High byte of the last row to clear. |

| (ARG4) | LASTL:                               | Low byte of the last row to clear.  |

This is a variable execution time command.

### 6.3.6 CLR\_SECT\_BRT\_IB

This command clears a given section of the display, less the active frame, to the bright state. The section is defined by the first and last rows (numbered 0 to 239). Any part of the active frame (left/right and top/bottom) in the defined section is set to the dark state, i.e. the border is inverted. The maximum number of rows that may be cleared using this command is 120. The command has 4 arguments.

| (CMD)  | 0x15:   | The command.                        |  |  |  |  |

|--------|---------|-------------------------------------|--|--|--|--|

| (ARG1) |         |                                     |  |  |  |  |

| (ARG2) | FIRSTL: | Low byte of the first row to clear  |  |  |  |  |

| (ARG3) | LASTH:  | High byte of the last row to clear. |  |  |  |  |

| (ARG4) | LASTL:  | Low byte of the last row to clear.  |  |  |  |  |

This is a variable execution time command.

### 6.3.7 CLR\_SECT\_DRK

This command clears a given section of the display to the dark state. The section is defined by the first and last rows (numbered 0 to 239). Any part of the active frame (left/right and top/bottom) in the defined section is also set to the dark state. The maximum number of rows that may be cleared using this command is 120. The command has 4 arguments.

| (CMD)  | 0x16:   | The command.                         |

|--------|---------|--------------------------------------|

| (ARG1) | FIRSTH: | High byte of the first row to clear. |

| (ARG2) | FIRSTL: | Low byte of the first row to clear   |

| (ARG3) | LASTH:  | High byte of the last row to clear.  |

| (ARG4) | LASTL:  | Low byte of the last row to clear.   |

This is a variable execution time command.

# 320×240×5.7 SPI

### 6.3.8 CLR\_SECT\_DRK\_IB

This command clears a given section of the display, less the active frame, to the dark state. The section is defined by the first and last rows (numbered 0 to 239). Any part of the active frame (left/right and top/bottom) in the defined section is set to the bright state, i.e. the border is inverted. The maximum number of rows that may be cleared using this command is 120. The command has 4 arguments.

| (CMD)                                        | The command. |                                     |  |  |  |

|----------------------------------------------|--------------|-------------------------------------|--|--|--|

| (ARG1) FIRSTH: High byte of the first row to |              |                                     |  |  |  |

| (ARG2)                                       | FIRSTL:      | Low byte of the first row to clear  |  |  |  |

| (ARG3)                                       | LASTH:       | High byte of the last row to clear. |  |  |  |

| (ARG4)                                       | LASTL:       | Low byte of the last row to clear.  |  |  |  |

This is a variable execution time command.

### 6.3.9 DISP\_FULLSCRN

This command triggers a full screen update from a specified image buffer in the onboard image RAM. The command has 2 arguments.

| (CMD)  | 0x18:     | The command.                                    |

|--------|-----------|-------------------------------------------------|

| (ARG1) | ADDRESSH: | High byte of the image buffer starting address. |

| (ARG2) | ADDRESSL: | Low byte of the image buffer starting address.  |

This is a variable execution time command.

### 6.3.10 DISP\_PARTSCRN

This command triggers a partial screen update from a specified image buffer in the onboard image RAM to a specified group of rows (numbered 0 to 239). The maximum number of rows permitted in a single partial screen update is 120. The command has 6 arguments.

| (CMD)  | 0x19:     | The command.                                    |

|--------|-----------|-------------------------------------------------|

| (ARG1) | ADDRESSH: | High byte of the image buffer starting address. |

| (ARG2) | ADDRESSL: | Low byte of the image buffer starting address.  |

| (ARG3) | FIRSTH:   | High byte of the first row to update.           |

| (ARG4) | FIRSTL:   | Low byte of the first row to update.            |

| (ARG5) | LASTH:    | High byte of the last row to update.            |

| (ARG6) | LASTL:    | Low byte of the last row to update.             |

This is a variable execution time command.

### 6.4 System Control Commands

The system control commands are used to configure display module operation and obtain display module information and status.

### 6.4.1 SLEEP

This command puts the display module in the low power sleep mode. There are no arguments.

(CMD) 0x20: The command.

# 320×240×5.7 SPI

### 6.4.2 **RESET**

This command triggers a software reset of the display module. There are no arguments.

(CMD) 0x24: The command.

See Section 4.3 for details of the reset sequence.

### 6.4.3 GET\_FW\_VERSION

This command retrieves the firmware version of the display module. The firmware version is returned as a fixed-length, NULL terminated ASCII string. The command requires 35 dummy arguments to clock out the version string.

| (CMD)   | 0x26:    | The command. |

|---------|----------|--------------|

| (ARG1)  | DUMMY1:  | Don't Care   |

|         | •        |              |

|         | •        |              |

|         | •        |              |

| (ARG35) | DUMMY35: | Don't Care   |

The bytes returned while clocking in the command, ARG1, and ARG2 are to be ignored. The first byte of the version string is returned with ARG3 and continues with subsequent bytes. The version string has the following format:

"FFFFR-LCID/MMM DD YYYY/HH:MM:SS"

- FFFFF: Firmware identifier.

- R: Revision letter.

- LCID: Liquid crystal material identifier.

- MMM: Compile date month identifier.

- DD: Compile date day identifier.

- YYYY: Compile date year identifier.

- HH: Compile time hour identifier.

- MM: Compile time minute identifier.

- SS: Compile time second identifier.

- NULL: '0'

### 6.4.4 SET\_CONTRAST

This command permits the contrast of the display module to be adjusted. The command has one argument.

| (CMD)  | 0x27:     | The command.          |

|--------|-----------|-----------------------|

| (ARG1) | CONTRAST: | The contrast setting. |

The contrast setting is a signed 2's complement value. Thus, it can range from -128 to +127. A setting of zero produces the default contrast. This should generally be suitable as the display modules have integrated temperature compensation and are calibrated at the factory. Positive contrast values brighten the display, while negative values darken the display. The magnitude of the contrast value determines the amount of contrast adjustment, with higher magnitudes producing the larger effect.

The contrast setting is stored in RAM and resets to zero when power is cycled or the RESET command is issued.

# 320×240×5.7 SPI

### 6.4.5 ELEC\_ERASE

The electronic erase command removes pressure points from the display (see Section 4.4). There are no arguments. See the warning in Section 4.4 about the proper use of this command.

(CMD) 0x2A: The command.

This is a variable execution time command.

### 7 Optional Heater

The 320x240 display module may be ordered with an optional integrated heater. Modules with the heater have an extended operating temperature range and improved update speeds at low ambient temperatures. The heater requires an external 12V power supply connection at the J2 header location on the display PCB module, (see Sect.5.4). Note the polarity specified at the J2 header location. Incorrectly wiring the 12V power supply will damage the heater. Refer to the "Display Heater Option" Application Note (25091) for additional information.

### Heater Specifications:

| Parameter                 | Minimum | Typical | Maximum | Units |

|---------------------------|---------|---------|---------|-------|

| Resistance                | -       | 4.9     | -       | Ω     |

| Voltage                   | -       | -       | 12      | V     |

| Peak Current <sup>1</sup> | -       | 2.5     | -       | A     |

| Peak Power <sup>1</sup>   | -       | 30      | -       | W     |

Consumed at temperatures more than 10 degrees C below the set point. At temperatures where PWM is active, the average is lower but the peak remains the same.

Inclusion of the optional heater results in several changes to the module specifications and additions to the instruction set. These changes and additions are given as follows:

### Heater Changes to General Specifications (Sect. 5.1):

| Parameter                   | Description                                        |

|-----------------------------|----------------------------------------------------|

| Display Module Weight       | 42 grams (Weight is 52 grams with optional bezel.) |

| Operating Temperature Range | -20°C to +60°C                                     |

### Heater Changes to Electrical Specifications (Sect. 5.2):

| Parameter                    |                         | Minimum | Typical | Maximum | Units |

|------------------------------|-------------------------|---------|---------|---------|-------|

| Standby Current <sup>2</sup> | V <sub>CC</sub> (=3.3V) | -       | 875     | -       | μA    |

| Sleep Current <sup>2</sup>   | V <sub>CC</sub> (=3.3V) | -       | 775     | -       | μA    |

Current values when heater circuit is enabled, due to temperature monitoring by microprocessor.

### Heater Changes to Timing Specifications (Sect. 5.5):

| Symbol           | Parameter     | Min. | Max. | Units |

|------------------|---------------|------|------|-------|

| f <sub>SCK</sub> | SCK Frequency | -    | 200  | kHz   |

### **KENT** INCORPORATED

### Heater Additions to Instruction Set (Sect. 6.1):

| Function | Command                      | Hex | Description                                        | Details    |

|----------|------------------------------|-----|----------------------------------------------------|------------|

|          |                              |     | Description                                        | # of Bytes |

| Heater   | HEATER_DISABLE               | 2C  | Disable the heater.                                | 1          |

|          | HEATER_ENABLE <sup>1</sup>   | 2D  | Enable the heater to regulate to desired setpoint. | 1          |

|          | HEATER_SET_TEMP <sup>1</sup> | 2E  | Program the heater setpoint.                       | 2          |

<sup>1</sup> – Variable Execution Time Command

#### HEATER\_DISABLE

This command completely disables the heater. There are no arguments.

(CMD) 0x2C: The command.

#### HEATER\_ENABLE

This command enables the heater. With the heater enabled, the display module automatically regulates the heater output to achieve the desired temperature setpoint. The amount of heat output by the heater at a given time depends on the current display temperature and the heater setpoint.

(CMD) 0x2D: The command.

This is a variable execution time command.

#### HEATER\_SET\_TEMP

This command permits the temperature setpoint of the heater to be specified. When the heater is enabled, the module will automatically adjust the display temperature to this setpoint.

(CMD)0x2E:The command.(ARG1)SETPOINT:The temperature setpoint in °C (-20 to +40).

The setpoint parameter is a signed 2's complement value. Thus, it can range from -128 to +127. However, the module limits the maximum value to 40 °C and values below -20 °C are generally not useful.

Caution must be exercised that power to the display module is not removed while this command is executing. Otherwise, the flash-based heater lookup table generated by the command may become corrupted. Typically, this command is used a single time at device fabrication and never reissued.

This is a variable execution time command.

#### Heater Electrical Connections:

The heater must be powered from an external 12V source connected to the J2 header location on the display module printed circuit board. Pin 1 is the positive terminal (nearest to the J1 connector), and pin 2 is the negative terminal (refer to the "Display Heater Option Application Note" - 25091). *Note: the negative terminal must be externally referenced to the display module ground in order for the transistor which regulates the heater to switch.*

5,636,044, 5,644,330, 5,251,048, 5,384,067, 5,437,811, 5,453,863, 5,668,614, 5,691,796, 5,695,682, 5,748,277, 5,766,694, 5,847,798 and numerous other patent applications by Kent Display Systems, Inc., Kent Displays, Inc. and Kent State University pending in the U.S. and in foreign patent filings include: PCT, Canada, China, Europe, Israel, Japan, Korea, and Taiwan among others.