# STN1110

# Multiprotocol OBD to UART Interpreter Datasheet

# **Table of Contents**

| 1.0   | Overview                                    | 3  |

|-------|---------------------------------------------|----|

| 2.0   | Feature Highlights                          | 3  |

| 3.0   | Typical Applications                        | 3  |

| 4.0   | Pinout                                      |    |

| 4.1   | Pinout Summary                              | 5  |

| 4.2   | Detailed Pin Descriptions                   | 6  |

| 5.0   | Guidelines for Getting Started with STN1110 | 8  |

| 5.1   | Basic Connection Requirements               | 8  |

| 5.2   | Decoupling Capacitors                       | 8  |

| 5     | 5.2.1 Tank Capacitors                       | 8  |

| 5.3   | AVDD and AVss Pins                          |    |

| 5.4   | Internal Voltage Regulator Filter Capacitor | 8  |

| 5.5   | Device Reset Pin                            | 9  |

| 5.6   | Oscillator Pins                             | 9  |

| 5.7   | NVM Reset Input                             | 9  |

| 5.8   | Open Drain Outputs                          |    |

| 6.0   | Reference Schematics                        | 10 |

| 6.1   | Recommended Minimum Connection              | 10 |

| 6.2   | Typical Configuration                       |    |

| 7.0   | Electrical Characteristics                  |    |

| 7.1   | Absolute Maximum Ratings                    |    |

| 7.2   | Electrical Characteristics                  |    |

| 8.0   | Packaging Diagrams and Parameters           |    |

| 8.1   | SPDIP (SP) Package                          |    |

| 8.2   | SOIC 300mil (SO) Package                    |    |

| 8.3   | SOIC 300mil (SO) Land Pattern               |    |

| 8.4   | QFN-S (MM) Package                          |    |

| 8.5   | QFN-S (MM) Land Pattern                     |    |

| 9.0   | Ordering Information                        |    |

|       | ndix A: Revision History                    |    |

| Apper | ndix B: Contact Information                 | 22 |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your OBD Solutions products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please visit our web site at http://www.obdsol.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., STN111DSA is version A of document STN1110DS).

#### All rights Reserved. Copyright © 2010 OBD Solutions

Every effort is made to verify the accuracy of information provided in this document, but no representation or warranty can be given and no liability assumed by OBD Solutions with respect to the accuracy and/or use of any products or information described in this document. OBD Solutions will not be responsible for any patent infringements arising from the use of these products or information, and does not authorize or warrant the use of any OBD Solutions product in life support devices and/or systems. OBD Solutions reserves the right to make changes to the device(s) described in the document in order to improve reliability, function, or design.

# 1.0 Overview

This datasheet summarizes the features of the STN1110 device. It is not intended as a comprehensive reference source. To complement the information in this datasheet refer to the **"STN1100 Family Reference and Programming Manual"**. Please see the OBD Solutions website (<u>www.obdsol.com</u>) for the latest version of the STN1100 Family Reference Manual.

On-Board Diagnostics, Second Generation (OBD-II) is a set of standards for implementing a computer based system to control emissions from vehicles. It was first introduced in the United States in 1994, and became a requirement on all 1996 and newer US vehicles. Other countries, including Canada, parts of the European Union, Japan, Australia, and Brazil adopted similar legislation. A large portion of the modern vehicle fleet supports OBD-II or one of its regional flavors (EOBD, JOBD, etc).

Among other things, OBD-II requires that each compliant vehicle be equipped with a standard diagnostic connector (DLC) and describes a standard way of communicating with the vehicle's computer, also known as the ECU (Electronic Control Unit).

# 2.0 Feature Highlights

- Fully compatible with the ELM327 AT command set

- Extended ST command set

- UART interface (baud rates from 38 bps to 10 Mbps<sup>1</sup>)

- Secure bootloader for easy firmware updates

- Support for all legislated OBD-II protocols:

- o ISO 15765-4 (CAN)

- ISO 14230-4 (Keyword Protocol 2000)

- ISO 9141-2 (Asian, European, Chrysler vehicles)

- SAE J1850 VPW (GM vehicles)

- SAE J1850 PWM (Ford vehicles)

- Support for non-legislated OBD protocols:

- o ISO 15765

- ISO 11898 (raw CAN)

- Support for SAE J1939 OBD protocol

- Superior automatic protocol detection algorithm

- Large memory buffer

- Voltage input for battery monitoring

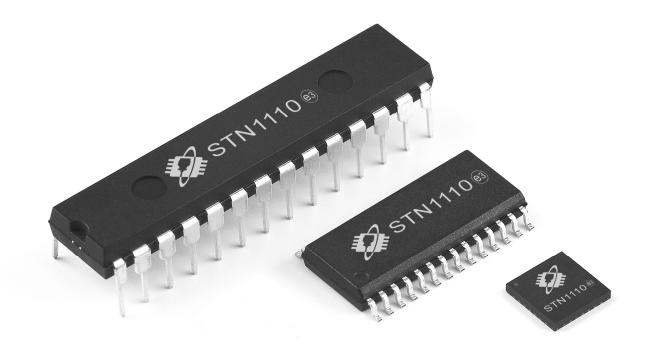

- Available in SPDIP, SOIC and QFN-S packages

- **RoHS** compliant

# 3.0 Typical Applications

- Academic projects

- Automotive diagnostic scan tools and code readers

- Digital dashboards

- Fleet management and tracking applications

- OBD data loggers

A wealth of information can be obtained by tapping into the OBD bus, including the status of the malfunction indicator light (MIL), diagnostic trouble codes (DTCs), inspection and maintenance (I/M) information, freeze frames, VIN, hundreds of real-time parameters, and more.

The STN1110 integrated circuit is an OBD to UART interpreter that can be used to convert messages between any of the OBD-II protocols currently in use, and UART. It is fully compatible with the *de facto* industry standard ELM327 command set. Based on a 16-bit processor core, the STN1110 offers more features and better performance than any other ELM327 compatible IC.

**Note 1:** Maximum theoretical baud rate. Actual maximum baud rate is application dependent and may be limited by driver hardware.

# 4.0 Pinout

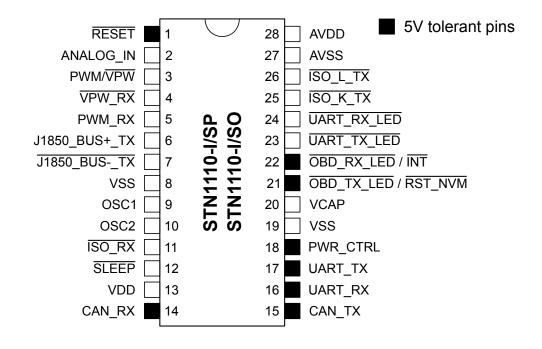

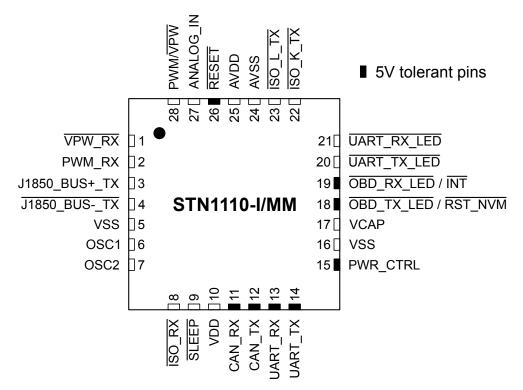

# 28-Pin QFN-S<sup>(1)</sup>

Note 1. The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to VSs externally.

# 4.1 Pinout Summary

| Pin Number    |       |                      |          |                                                                                                                            |  |

|---------------|-------|----------------------|----------|----------------------------------------------------------------------------------------------------------------------------|--|

| SOIC<br>SPDIP | QFN-S | Pin Name             | Pin Type | Pin Description                                                                                                            |  |

| 1             | 26    | RESET                | I, 5V    | Active low device reset input                                                                                              |  |

| 2             | 27    | ANALOG_IN            | Α        | Analog voltage measurement input                                                                                           |  |

| 3             | 28    | PWM/VPW              | 0        | SAE J1850 PWM/VPW Bus+ voltage select output                                                                               |  |

| 4             | 1     | VPW_RX               | I        | Active low J1850 VPW receive input                                                                                         |  |

| 5             | 2     | PWM_RX               | I        | SAE J1850 PWM receive input                                                                                                |  |

| 6             | 3     | J1850_BUS+_TX        | 0        | SAE J1850 Bus+ transmit output                                                                                             |  |

| 7             | 4     | J1850_BUSTX          | 0        | Active low SAE J1850 Bus- transmit output                                                                                  |  |

| 8             | 5     | VSS                  | Р        | Ground reference for logic and I/O pins                                                                                    |  |

| 9             | 6     | OSC1                 | I        | 16.000 MHz oscillator crystal input                                                                                        |  |

| 10            | 7     | OSC2                 | 0        | 16.000 MHz oscillator crystal output                                                                                       |  |

| 11            | 8     | ISO_RX               | I        | Active low ISO 9141/ISO 14230 K-line input                                                                                 |  |

| 12            | 9     | SLEEP                | I        | External sleep control input                                                                                               |  |

| 13            | 10    | VDD                  | Р        | Positive supply for logic and I/O pins                                                                                     |  |

| 14            | 11    | CAN_RX               | I, 5V    | CAN receive input                                                                                                          |  |

| 15            | 12    | CAN_TX               | OD, 5V   | CAN transmit output                                                                                                        |  |

| 16            | 13    | UART_RX              | I, 5V    | UART receive input                                                                                                         |  |

| 17            | 14    | UART_TX              | OD, 5V   | UART transmit output                                                                                                       |  |

| 18            | 15    | PWR_CTRL             | OD, 5V   | External power control output                                                                                              |  |

| 19            | 16    | VSS                  | Р        | Ground reference for logic and I/O pins                                                                                    |  |

| 20            | 17    | VCAP                 | Р        | CPU logic filter capacitor connection                                                                                      |  |

| 21            | 18    | OBD_TX_LED / RST_NVM | OD/I, 5V | Active low OBD transmit activity LED output <i>and</i> active low input to reset non-volatile settings to factory defaults |  |

| 22            | 19    | OBD_RX_LED / INT     | OD/O, 5V | Active low OBD receive activity LED or interrupt output                                                                    |  |

| 23            | 20    | UART_TX_LED          | 0        | Active low UART transmit activity LED output                                                                               |  |

| 24            | 21    | UART_RX_LED          | 0        | Active low UART transmit activity LED output                                                                               |  |

| 25            | 22    | ISO_K_TX             | 0        | Active low ISO 9141/ISO 14230 K-line output                                                                                |  |

| 26            | 23    | ISO_L_TX             | 0        | Active low ISO 9141/ISO 14230 L-line output                                                                                |  |

| 27            | 24    | AVSS                 | Р        | Analog ground reference                                                                                                    |  |

| 28            | 25    | AVDD                 | Р        | Analog positive supply                                                                                                     |  |

Legend:

I – Schmitt trigger input with CMOS levels A – analog input

O – digital output OD – open drain output

5V - 5 volt tolerant pin

P – power pin

# 4.2 Detailed Pin Descriptions

### RESET

Device reset input. A logic low pulse (min 2  $\mu$ s) on this pin will reset the device. Apply a continuous logic low to hold the device in reset. If your circuit does not use this functionality, connect this pin to VDD.

#### ANALOG\_IN

Analog voltage measurement input (AVDD max). By default, this input is calibrated for an external  $62k\Omega/10k\Omega$  voltage divider connected to battery positive. Connect to AVSS if unused.

#### PWM / VPW

The firmware uses this pin to control the voltage level of the SAE J1850 PWM/VPW Bus+ supply. When the PWM protocol is selected, it outputs a logic high to switch the supply voltage to a nominal 5V. When the VPW protocol is selected, it outputs a logic low to switch the supply voltage to a nominal 8V. Leave unconnected if unused.

#### VPW\_RX

Active low SAE J1850 VPW receive input. When the SAE J1850 Bus+ is in the recessive (low) state, this pin should be at a logic high level. When the SAE J1850 Bus+ is in the dominant (high) state, this pin should be at a logic low level. Pull up to VDD if unused.

#### PWM\_RX

SAE J1850 PWM receive input. When the SAE J1850 bus is in the recessive state (Bus+ is low, Bus- is high), this pin should be at a logic low level. When the SAE J1850 bus is in the dominant (Bus+ is high) state, this pin should be at a logic high level. Pull up to VDD if unused.

#### J1850\_BUS+\_TX

SAE J1850 Bus+ transmit output. When the pin is high, Bus+ should be high (dominant). Leave unconnected if unused.

#### J1850\_BUS-\_TX

Active low SAE J1850 Bus- transmit output. When the pin is high, Bus- should be low (dominant). Leave unconnected if unused.

#### VSS

Ground reference for logic and I/O pins.

#### OSC1, OSC2

16.000 MHz oscillator crystal connection.

#### ISO\_RX

Active low ISO 9141/ISO 14230 K-line receive input. When K-line is high (recessive), this pin should be at a logic low level. Connect to VSS if unused.

#### SLEEP

External sleep control input. When enabled in firmware, puts the device into low-power sleep mode. Polarity of this pin can be configured in firmware; default configuration is active low. Internal pull-up to VDD is enabled by default, but can be disabled in firmware. Leave unconnected if unused.

#### VDD

Positive 3.0 – 3.6V supply for logic and I/O pins.

#### CAN\_RX

CAN receive input. Must be connected to a CAN transceiver IC. Compatible with +3.3V and +5V logic. Pull up to VDD if unused.

#### CAN\_TX

CAN transmit output. Must be connected to a CAN transceiver IC. Open drain – requires a pull-up to VDD or +5V (12 mA max). Pull-up resistor value depends on CAN baud rates used and the trace length (higher resistor values can be used with lower baud rates and shorter traces); recommended value is 1 k $\Omega$ . Pull up to VDD via 100 k $\Omega$  resistor if unused.

# UART\_RX

UART receive input. Compatible with +3.3V and +5V logic.

# UART\_TX

UART transmit output. Open drain – requires a pull-up to VDD or +5V (4 mA max). Pull-up value depends on UART baud rate and the trace length (higher resistor values can be used with lower baud rates and shorter traces); typical value is  $4.7 \text{ k}\Omega$ .

#### PWR\_CTRL

External power control output. Used to switch external circuitry into low-power (sleep) state. Polarity can be configured in firmware; default configuration is active high (logic low = sleep mode). Open drain – requires a pull-up to VDD or +5V (12 mA max); be mindful of the fact that the pull-up will draw current in low-power state. Pull up to VDD via 100 k $\Omega$  resistor if unused.

#### VCAP

CPU logic filter capacitor connection. Must be connected to a low-ESR (<  $5\Omega$ ) minimum 4.7  $\mu$ F capacitor; typical value is 10  $\mu$ F.

# OBD\_TX\_LED / RST\_NVM

Active low OBD transmit activity LED output (12 mA max) and active low input to reset NVM to factory defaults. Open drain – requires a pull-up to VDD or +5V (12 mA max) if not pulled up via an LED connection. Pull up to VDD if unused.

# OBD\_RX\_LED / INT

Active low OBD receive activity LED *or* interrupt output (12 mA max). Open drain by default (requires a pull-up to VDD or +5V when configured as interrupt); can be configured as a digital output. If unused, pull up to VDD or configure as digital output and leave unconnected.

# UART\_TX\_LED

Active low UART transmit activity LED output (4 mA max). Voltage on the anode of the LED must not exceed VDD + 0.3V. Leave unconnected if unused.

#### UART\_RX\_LED

Active low UART transmit activity LED output (4 mA max). Voltage on the anode of the LED must not exceed VDD + 0.3V. Leave unconnected if unused.

# ISO\_K\_TX

Active low ISO 9141/ISO 14230 K-line output. When the pin is logic high, K-line should be low. Leave unconnected if unused.

#### ISO\_L\_TX

Active low ISO 9141/ISO 14230 L-line output. When the pin is logic high, L-line should be low. Leave unconnected if unused.

#### AVSS

Analog ground reference. Must be connected to analog "clean" ground (between VSS – 0.3V and VSS + 0.3V) or VSS.

#### AVDD

Analog positive supply. Must be connected to VDD or an external voltage reference (between VDD - 0.3V or 3.0V, whichever is greater and VDD + 0.3V or 3.6V, whichever is lesser). AVDD may be decoupled from digital supply by connecting it to VDD via a 10  $\Omega$ resistor.

# 5.0 Guidelines for Getting Started with STN1110

# 5.1 Basic Connection Requirements

Getting started with the STN1110 IC requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- VDD and both Vss pins (see Section 5.2 "Decoupling Capacitors")

- AVDD and AVSS pins (see Section 5.2 "Decoupling Capacitors" and Section 5.3 "AVDD and AVSS Pins")

- VCAP (see Section 5.4 "Internal Voltage Regulator Filter Capacitor")

- **RESET** pin (see Section 5.5 "Device Reset Pin")

- OSC1 and OSC2 pins (see Section 5.6 "Oscillator Pins")

- **RST\_NVM** pin (see Section 5.7 "NVM Reset Input")

- **Open Drain Output Pull-ups** (see Section 5.8 "Open Drain Outputs")

# 5.2 Decoupling Capacitors

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS and AVDD, AVSS is required. Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: Recommendation of 1 µF, 10-20V. This capacitor should be a low-ESR and have resonance frequency in the range of 20 MHz and higher. It is recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within 1/4" (6 mm) in length.

- Handling high frequency noise: If the board is experiencing high frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of  $0.01 \, \mu$ F to  $0.001 \, \mu$ F. Place this second capacitor next to the primary decoupling capacitor.

• Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum thereby reducing PCB track inductance.

# 5.2.1 Tank Capacitors

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits, including STN1110, to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device, and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

# 5.3 AVDD and AVss Pins

As a minimum, AVDD must be connected directly to VDD and AVSS must be connected to directly VSS.

It is recommended that AVDD be connected to to VDD via a 10  $\Omega$  resistor or a small (10  $\mu H$  – 47  $\mu H)$  inductor.

AVss should be connected to the electrically cleanest ground net (plane). For best results, analog circuitry should have a separate ground plane with a point connection to Vss ground plane as close as possible to the AVss pin.

# 5.4 Internal Voltage Regulator Filter Capacitor

A low-ESR (< 5  $\Omega$ ) capacitor is required on the VCAP pin, which is used to stabilize the internal voltage regulator output voltage. The VCAP pin must not be connected to VDD, and must have a capacitor between 4.7 µF and 10 µF, 16V connected to ground. The type can be ceramic or tantalum. Refer to **Section 7.2 "Electrical Characteristics"** for additional information. The placement of this capacitor should be close to the VCAP pin. It is recommended that the trace length not exceed 1/4" (6 mm).

# 5.5 Device Reset Pin

**RESET** pin must be logic high for STN1110 to run. If this pin is not controlled by the host controller, it must be connected to VDD.

It is recommended to pull up  $\overrightarrow{\text{RESET}}$  pin to VDD via a 10 k $\Omega$  resistor.

# 5.6 Oscillator Pins

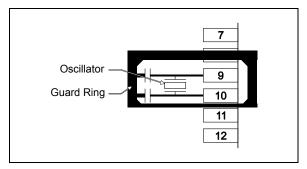

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the STN1110 ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is shown in Figure 1.

# Figure 1 – Suggested Placement of the Oscillator Circuit

# 5.7 NVM Reset Input

RST\_NVM pin must be pulled up to VDD via a 10 k $\Omega$  resistor for proper device operation.

If OBD\_TX\_LED / RST\_NVM pin is used to directly drive an LED, the pull-up is unnecessary.

# 5.8 Open Drain Outputs

All open drain outputs (as specified in section 4.1) that are in use must be pulled up to VDD or +5V. Specifically, UART\_TX pin must be pulled up in order to be able to communicate with the device.

See section 4.2 "Detailed Pin Descriptions" for more information.

# 6.0 **Reference Schematics**

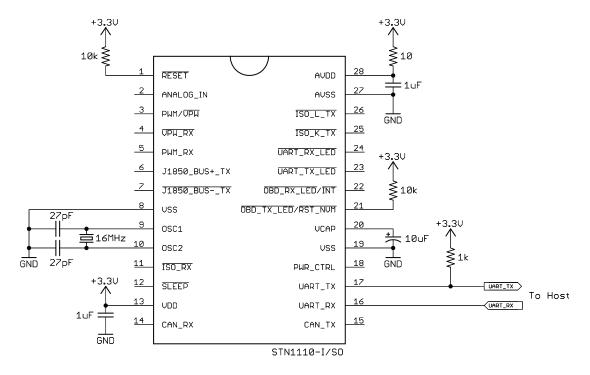

# 6.1 Recommended Minimum Connection

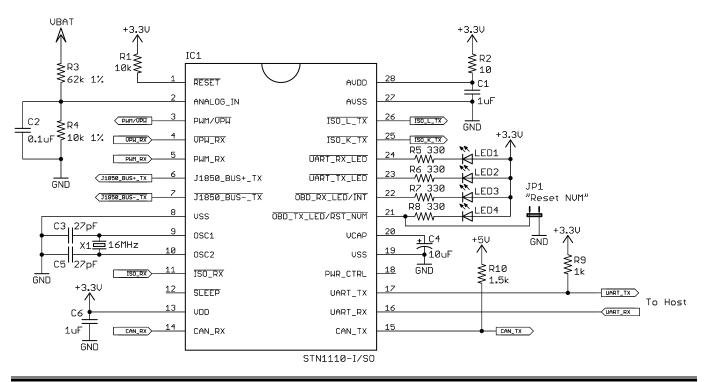

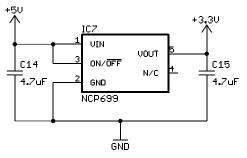

# 6.2 Typical Configuration

#### Figure 2 – STN1110 IC

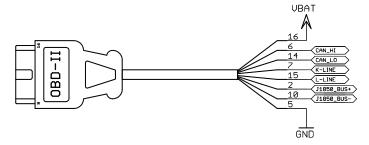

#### Figure 3 – OBD Connections

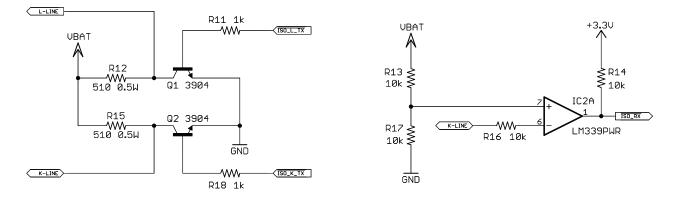

Figure 4 – ISO Transceiver

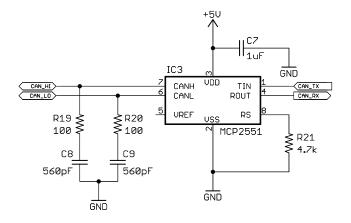

### Figure 5 – CAN Transceiver

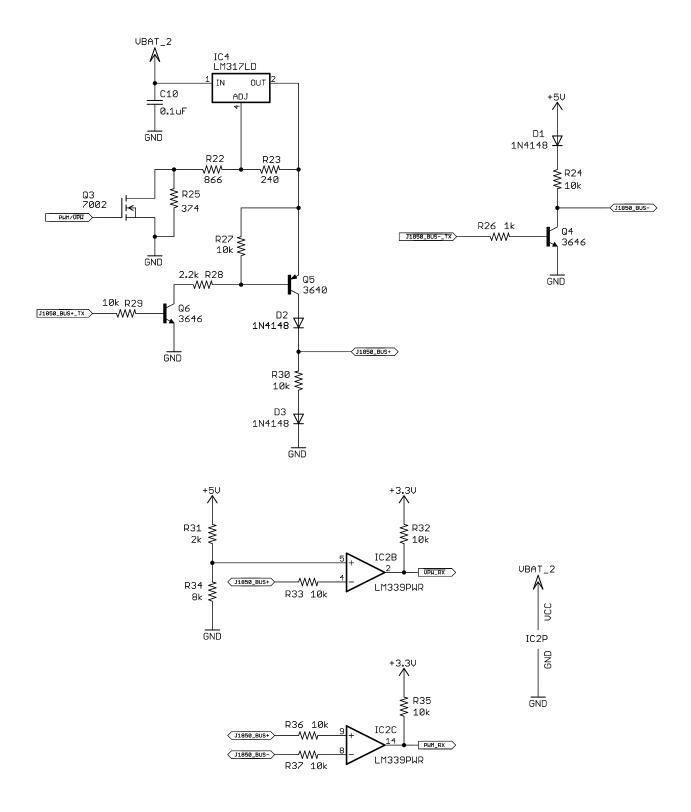

#### Figure 6 – J1850 Transceiver

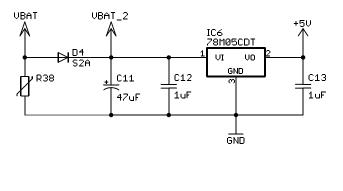

# Figure 7 – Power Supplies

# 7.0 Electrical Characteristics

This section provides an overview of STN1110 electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

STN1110 integrated circuit is based on PIC24HJ128GP502 device from Microchip Technology. For more detailed device specifications or clarification, refer to Microchip documentation, available at <a href="http://www.microchip.com">http://www.microchip.com</a>.

# 7.1 Absolute Maximum Ratings<sup>(1)</sup>

| Storage temperature                                                            |                |

|--------------------------------------------------------------------------------|----------------|

| Ambient temperature under bias                                                 |                |

| Voltage on VDD with respect to Vss                                             | -0.3V to +4.0V |

| Voltage on any pin that is not 5V tolerant with respect to Vss <sup>(2)</sup>  |                |

| Voltage on any 5V tolerant pin with respect to Vss when $VDD \ge 3.0V^{(2)}$ . |                |

| Voltage on any 5V tolerant pin with respect to Vss when $VDD < 3.0V^{(2)}$ .   |                |

| Maximum current sourced/sunk by PWM/VPW, CAN_TX, UART_TX,                      |                |

| PWR_CTRL, OBD_TX_LED, and OBD_RX_LED / INT outputs                             | 12 mA          |

| Maximum current sourced/sunk by any other output                               |                |

|                                                                                |                |

**Note** 1. Stresses beyond those listed here can cause permanent damage to the device. These are stress ratings only, and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods can affect device reliability.

2. See "Pin Summary" section for the list of 5V tolerant pins.

# 7.2 Electrical Characteristics

| Sym | Characteristic                       | Min | Тур | Мах  | Units | Conditions |

|-----|--------------------------------------|-----|-----|------|-------|------------|

| TJ  | Operating Junction Temperature       | -40 | _   | +125 | °C    |            |

| TA  | <b>Operating Ambient Temperature</b> | -40 | _   | +85  | °C    |            |

#### Table 2: Power Specifications

| Sym  | Characteristic                                                                               | Min                               | Typ <sup>(1)</sup> | Max                                          | Units | Conditions     |

|------|----------------------------------------------------------------------------------------------|-----------------------------------|--------------------|----------------------------------------------|-------|----------------|

| Vdd  | Supply Voltage                                                                               | 3.0                               | 3.3                | 3.6                                          | V     |                |

| VPOR | <b>VDD Start Voltage</b> <sup>(2)</sup><br>to ensure internal power-on reset<br>(POR) signal | _                                 | —                  | Vss                                          | V     |                |

| Svdd | <b>VDD Rise Rate</b> <sup>(3)</sup><br>to ensure internal power-on reset<br>(POR) signal     | 0.03                              | —                  | _                                            | V/ms  | 0–3.0V in 0.1s |

| AVDD | Analog Supply Voltage                                                                        | Greater of<br>VDD – 0.3<br>or 3.0 | _                  | Lesser of<br>V <sub>DD</sub> + 0.3<br>or 3.6 | V     |                |

| AVss | Analog Ground Reference                                                                      | Vss – 0.3                         | _                  | Vss + 0.3                                    | V     |                |

| VBOR | Brown-out Reset Voltage <sup>(4)</sup>                                                       | 2.40                              | _                  | 2.55                                         | V     |                |

|      | on VDD transition high-to-low                      |     |     |     |    |                        |

|------|----------------------------------------------------|-----|-----|-----|----|------------------------|

| Idd  | Operating Current <sup>(5)</sup>                   | —   | 60  | 90  | mA |                        |

| IPD  | Power-Down Current <sup>(5)</sup>                  | —   | 30  | 500 | μA | TA = -40°C, TA = +25°C |

|      |                                                    | —   | 130 | 750 | μA | TA = +85°C             |

| CEFC | External Filter Capacitor<br>connected to VCAP pin | 4.7 | 10  | _   | μF | ESR < 5 Ω              |

Note 1. Data in Typ column is at 3.3V, 25°C, unless otherwise stated

2. VDD voltage must remain at VSS for a minimum of 200 µs to ensure POR

3. This spec must be met in order to ensure that a correct internal power-on reset (POR) occurs. It is easily achieved using most common types of supplies, but may be violated if a supply with slowly varying voltage is used, as may be obtained through direct connection to solar sells or some charge pump circuits.

4. This parameter is for design guidance only and is not tested in manufacturing

5. STN1110 device current only. Does not include any load currents

| Sym | Characteristic                      | Min     | Typ <sup>(1)</sup> | Max     | Units | Conditions                |

|-----|-------------------------------------|---------|--------------------|---------|-------|---------------------------|

| VIL | Input Low Voltage                   |         |                    |         |       |                           |

|     | CAN_RX pin                          | Vss     | _                  | 0.3 Vdd | V     |                           |

|     | all other inputs                    | Vss     | —                  | 0.2 Vdd | V     |                           |

| VIH | Input High Voltage                  |         |                    |         |       |                           |

|     | not 5V tolerant pins <sup>(2)</sup> | 0.7 Vdd | _                  | Vdd     | V     |                           |

|     | 5V tolerant pins <sup>(2)</sup>     | 0.7 Vdd | —                  | 5.5     | V     |                           |

| Vin | ANALOG_IN Input Voltage             | AVss    | _                  | AVdd    | V     |                           |

| Vol | Output Low Voltage                  | _       | _                  | 0.4     | V     | IOL = 2 mA, VDD = 3.3V    |

| Vон | Output High Voltage                 | 2.4     | _                  | _       | V     | IOH = -2.3 mA, VDD = 3.3V |

| IPU | Internal Pull-up Current            | 50      | 250                | 400     | μA    | VDD = 3.3V, VPIN = VSS    |

Note 1. Data in Typ column is at 3.3V, 25°C, unless otherwise stated

2. See "Pin Summary" section for the list of 5V tolerant pins

#### Table 4: I/O Pin Timing Requirements

| Sym  | Characteristic                             | Min | Тур | Max   | Units | Conditions        |

|------|--------------------------------------------|-----|-----|-------|-------|-------------------|

| TRST | RESET Pulse Width (low)                    | 2   | —   | _     | μs    |                   |

| Тимм | Minimum UART Rx Pulse Width                | _   | 20  | —     | ns    | user setting < 15 |

|      | required for wakeup (user settable)        | 15  |     | 65534 | μs    | user setting ≥ 15 |

| Тѕтм | Minimum SLEEP Input Time                   |     | 15  |       | μs    | user setting = 0  |

|      | to stay high before wakeup (user settable) | 1   |     | 65534 | ms    | user setting > 0  |

# 8.0 Packaging Diagrams and Parameters

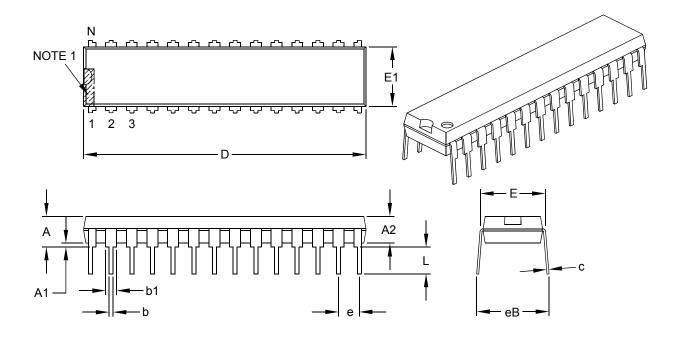

# 8.1 SPDIP (SP) Package

# 28-Lead Skinny Plastic Dual In-Line (SP) – 300 mil Body [SPDIP]

For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging.

|                            | Units         |       |          |       |

|----------------------------|---------------|-------|----------|-------|

| Dim                        | ension Limits | MIN   | NOM      | MAX   |

| Number of Pins             | Ν             |       | 28       |       |

| Pitch                      | е             |       | .100 BSC |       |

| Top to Seating Plane       | А             | —     | —        | .200  |

| Molded Package Thickness   | A2            | .120  | .135     | .150  |

| Base to Seating Plane      | A1            | .015  | —        | —     |

| Shoulder to Shoulder Width | E             | .290  | .310     | .335  |

| Molded Package Width       | E1            | .240  | .285     | .295  |

| Overall Length             | D             | 1.345 | 1.365    | 1.400 |

| Tip to Seating Plane       | L             | .110  | .130     | .150  |

| Lead Thickness             | с             | .008  | .010     | .015  |

| Upper Lead Width           | b1            | .040  | .050     | .070  |

| Lower Lead Width           | b             | .014  | .018     | .022  |

| Overall Row Spacing §      | eB            | —     | —        | .430  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

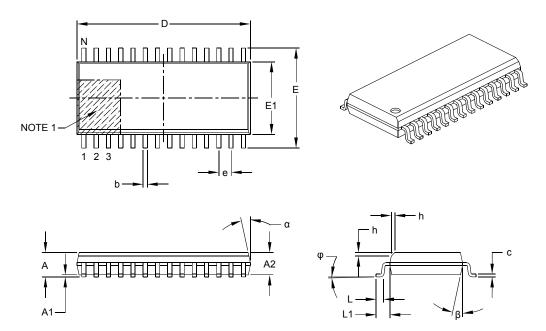

# 8.2 SOIC 300mil (SO) Package 28-Lead Plastic Small Outline (SO) – Wide, 7.50 mm Body [SOIC]

For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging.

|                          | Units            | MILLIMETERS |           |      |  |  |

|--------------------------|------------------|-------------|-----------|------|--|--|

|                          | Dimension Limits | MIN         | NOM       | MAX  |  |  |

| Number of Pins           | N                |             | 28        |      |  |  |

| Pitch                    | е                |             | 1.27 BSC  |      |  |  |

| Overall Height           | А                |             | —         | 2.65 |  |  |

| Molded Package Thickness | A2               | 2.05        | —         | —    |  |  |

| Standoff §               | A1               | 0.10        | —         | 0.30 |  |  |

| Overall Width            | E                | 10.30 BSC   |           |      |  |  |

| Molded Package Width     | E1               | 7.50 BSC    |           |      |  |  |

| Overall Length           | D                |             | 17.90 BSC |      |  |  |

| Chamfer (optional)       | h                | 0.25        | —         | 0.75 |  |  |

| Foot Length              | L                | 0.40        | —         | 1.27 |  |  |

| Footprint                | L1               |             | 1.40 REF  |      |  |  |

| Foot Angle Top           | φ                | 0°          | —         | 8°   |  |  |

| Lead Thickness           | С                | 0.18        |           | 0.33 |  |  |

| Lead Width               | b                | 0.31        |           | 0.51 |  |  |

| Mold Draft Angle Top     | α                | 5°          | _         | 15°  |  |  |

| Mold Draft Angle Bottom  | β                | 5°          | _         | 15°  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- $\ensuremath{\mathsf{BSC}}\xspace$  BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-052B

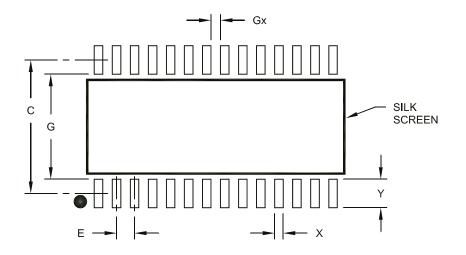

# 8.3 SOIC 300mil (SO) Land Pattern 28-Lead Plastic Small Outline (SO) – Wide, 7.50 mm Body [SOIC]

For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging.

**RECOMMENDED LAND PATTERN**

|                          | Units            |    | MILLIMETERS |      |      |

|--------------------------|------------------|----|-------------|------|------|

|                          | Dimension Limits |    | MIN         | NOM  | MAX  |

| Contact Pitch            |                  | Е  | 1.27 BSC    |      |      |

| Contact Pad Spacing      |                  | С  |             | 9.40 |      |

| Contact Pad Width (x28)  |                  | Х  |             |      | 0.60 |

| Contact Pad Length (x28) |                  | Y  |             |      | 2.00 |

| Distance Between Pads    |                  | Gx | 0.67        |      |      |

| Distance Between Pads    |                  | G  | 7.40        |      |      |

#### Notes:

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-2052A

<sup>1.</sup> Dimensioning and tolerancing per ASME Y14.5M.

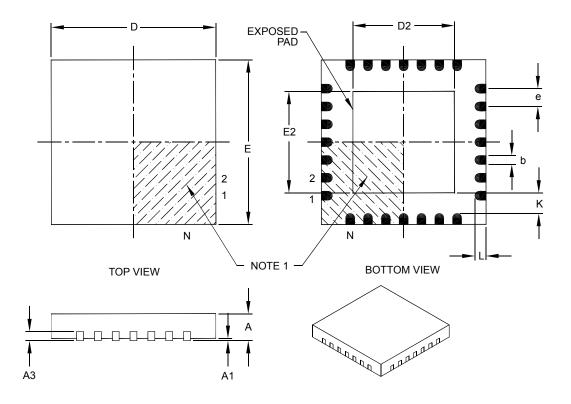

# 8.4 QFN-S (MM) Package 28-Lead Plastic Quad Flat, No Lead Package (MM) – 6x6x0.9 mm Body [QFN-S] with 0.40 mm Contact Length

For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging.

|                        | Units            | MILLIMETERS |      |      |

|------------------------|------------------|-------------|------|------|

| Dimensi                | Dimension Limits |             | NOM  | MAX  |

| Number of Pins         | Ν                | 28          |      |      |

| Pitch                  | е                | 0.65 BSC    |      |      |

| Overall Height         | А                | 0.80        | 0.90 | 1.00 |

| Standoff               | A1               | 0.00        | 0.02 | 0.05 |

| Contact Thickness      | A3               | 0.20 REF    |      |      |

| Overall Width          | E                | 6.00 BSC    |      |      |

| Exposed Pad Width      | E2               | 3.65        | 3.70 | 4.70 |

| Overall Length         | D                | 6.00 BSC    |      |      |

| Exposed Pad Length     | D2               | 3.65        | 3.70 | 4.70 |

| Contact Width          | b                | 0.23        | 0.38 | 0.43 |

| Contact Length         | L                | 0.30        | 0.40 | 0.50 |

| Contact-to-Exposed Pad | К                | 0.20        | —    | —    |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-124B

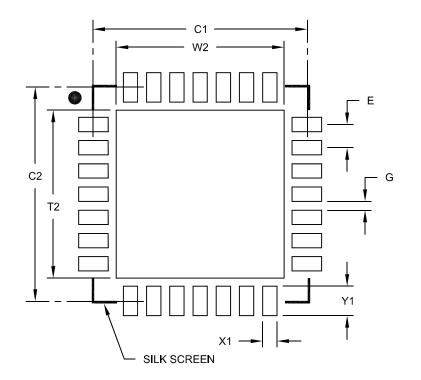

# 8.5 QFN-S (MM) Land Pattern

# 28-Lead Plastic Quad Flat, No Lead Package (MM) – 6x6x0.9 mm Body [QFN-S] with 0.40 mm Contact Length

For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging.

#### RECOMMENDED LAND PATTERN

|                            | Units            | MILLIMETERS |      |      |

|----------------------------|------------------|-------------|------|------|

|                            | Dimension Limits | MIN         | NOM  | MAX  |

| Contact Pitch              | E                | 0.65 BSC    |      |      |

| Optional Center Pad Width  | W2               |             |      | 4.70 |

| Optional Center Pad Length | T2               |             |      | 4.70 |

| Contact Pad Spacing        | C1               |             | 6.00 |      |

| Contact Pad Spacing        | C2               |             | 6.00 |      |

| Contact Pad Width (x28)    | X1               |             |      | 0.40 |

| Contact Pad Length (x28)   | Y1               |             |      | 0.85 |

| Distance Between Pads      | G                | 0.25        |      |      |

#### Notes:

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-2124

<sup>1.</sup> Dimensioning and tolerancing per ASME Y14.5M.

# 9.0 Ordering Information

| ТА             | Package    |      | Part Number  | SKU    |

|----------------|------------|------|--------------|--------|

| -40°C to +85°C | SPDIP (SP) | Tube | STN1110-I/SP | 365101 |

|                | SOIC (SO)  | Tube | STN1110-I/SO | 365111 |

|                | QFN-S (MM) | Tube | STN1110-I/MM | 365121 |

# **Appendix A: Revision History**

# Revision A (October 22, 2010)

Initial release of this document.

# **Appendix B: Contact Information**

OBD Solutions 1819 W Rose Garden Ln Ste 3 Phoenix, AZ 85027 United States

Phone:

+1 623.434.5506

Fax:

+1 623.321.1628

Email:

sales@obdsol.com

Web:

www.obdsol.com